采用FPGA實現發電機組頻率測量計的設計

3.2 二進制到十進制的轉換器模塊設計

本設計,需要轉換時鐘Convertfreq信號對轉換模塊進行時序控制,由于要在1s內完成轉換,則轉換時鐘Convertfreq的頻率應該選用高頻頻信號,即轉換時鐘Convertfreq的頻率是標準時鐘Samplefreq信號10分頻得到的。

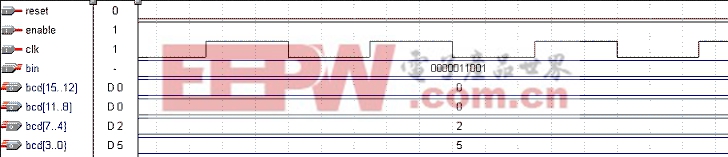

為了對本設計進行波形仿真,取輸入的10位二進制數bin[9..0]為10’b0000011001(十進制為25)。圖4為二進制到十進制的轉換器的仿真時序圖:

圖4 二進制到十進制的轉換器的仿真時序圖

4 仿真和調試

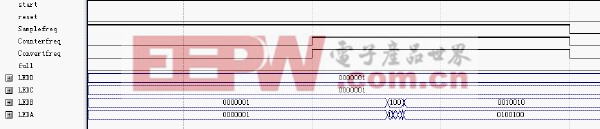

通過上述的描述,從各個模塊獨立的角度對其進行了仿真,結果表明設計符合要求。為了保證系統的整體可靠性,對整個系統做了仿真,仿真時序圖如圖5所示:

圖5 系統仿真時序圖

其中,LEDD,LEDC,LEDB,LEDA是譯碼的結果要在7段數碼管上顯示,0010010(顯示為2)、0100100(顯示為5)。將設計的頻率測量計下載到目標芯片EP1C3T144C6中,并在GW48實驗箱上進行的模擬仿真,當輸入頻率為1 Hz~1023 Hz的信號時,頻率測量計所測的頻率完全準確,當頻率高于1023Hz時,系統報警,同時頻率顯示為0。

5 結束語

基于FPGA設計的發電機組頻率測量計,系統在整體上采用光電耦合器的隔離方式,提高系統的抗干擾能力和穩定性。該系統具有線路簡單可靠、通用性強、穩定度高等優點,可廣泛應用于頻率電壓變換器、轉速繼電器。該設計的FPGA數字系統部分使用Verilog HDL語言,給出核心程序,并可以通過Verilog HDL語言的綜合工具進行相應硬件電路的生成,具有傳統邏輯設計方法所無法比擬的優越性。經過仿真后,驗證設計是成功的, 達到預期結果。同時這種方法設計的數字電子系統可移植性強、可更改性好。如果需要的頻率測量范圍需要擴大,不需要硬件變化只需改變軟件就可以,相對非常方便。

評論