利用FPGA實現HDB3編解碼功能

摘要:HDB3(三階高密度雙極性)碼具有無直流分量、低頻成分少、連零個數不超過3個、便于提取時鐘信號等特點。通過對HDB3編解碼原理進行分析和研究,提出一種基于FPGA的HDB3編解碼實現方法,給出Verilog HDL語言的實現方法和仿真波形,完成硬件電路的設計和測試,采用該方法設計的HDB3編解碼器已應用于相關實驗設備中。

關鍵詞:HDB3編碼;HDB3解碼;FPGA;Verilog HDL

1 引言

數字通信系統的某些應用可對基帶信號不載波調制而直接傳輸,其中傳輸線路對碼型的要求如下:信碼中不宜有直流分量,低頻分量應盡可能的少,碼型要便于時鐘信號提取。根據這些要求,ITU-T(國際電聯)在G.703建議中規定,對于2 MHz、8 MHz、32 MHz速率的數字接口均采用HDB3(三階高密度雙極性)碼。HDB3碼具有無直流分量,低頻成分少,連零個數不超過3個等特點,便于時鐘信號的提取和恢復,適合在信道中直接傳輸。這里利用Verilog HDL語言設計用于數字通信系統中的HDB3編解碼器。

2 HDB3編碼模塊設計

要設計一個實用的編碼模塊,首先要深入研究其編碼規則及其特點,然后根據編碼規則設計符合電路特性的編碼流程。HDB3碼的編碼規則包括:①將消息代碼變換成AMI碼,AMI碼的編碼規則是對碼流中的非“0”符號進行正負交替;②檢查AMI碼中的連零情況,當連零的個數小于4個時,保持AMI的形式不變;當連零的個數達到4個或超過4個時,則將非零碼后的第4個“0”替換成V碼,其中V碼的極性與前一非零碼(+1或-1)的極性保持一致,例如,前面的非零碼是+1,則將V碼記為+V;③完成插V操作后,檢查2個相鄰V碼之間非零碼的個數是否為偶數,若為偶數,則再將相鄰2個V碼中后一個V碼的前一非零碼后的第一個“0”變為B碼,B碼的極性與前一非“0”碼的極性相反,同時B碼后面的非“0”碼極性再次進行交替變換,保證極性交替反轉特性。

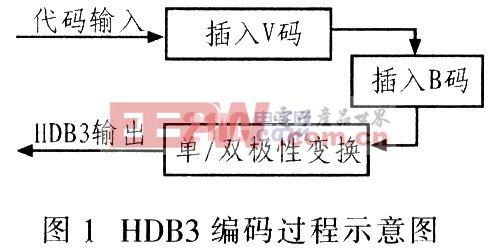

編碼規則中出現的V碼、B碼只是作為標識符,最終的電路實現還是“0”和“1”這兩種邏輯電平,因此需要采用二進制編碼對“1”、“0”、V、B進行編碼,“00”表示“0”、“0l”表示“1”,“10”表示B,“11”表示V。根據編碼規則和利用FPGA實現的特點,將編碼過程:首先插入V碼,然后插入B碼,最后是單雙極性變換。如果按照編碼規則的順序設汁.應該首先進行單雙極性變換,在完成插V和插B后,還需根據編碼規則變換當前B碼之后的非零碼的極性,這需要大量的寄存器來保存當前數據的狀態,導致電路非常復雜,占用大量的FPGA內部邏輯單元,實現難度大,且成本高。HDB3編碼過程示意圖如圖l所示。

評論