基于FPGA的雙口RAM與PCI9O52接口設(shè)計(jì)

當(dāng)狀態(tài)機(jī)處于讀空閑狀態(tài)時(shí),在每次上升沿采樣到ADS有效和LW R為低電平,且訪問雙口RAM空間(CS0或CSl有效),狀態(tài)機(jī)轉(zhuǎn)到讀開始狀態(tài)。接著是讀等待數(shù)據(jù)狀態(tài),此時(shí)根據(jù)片選信號CS0和CSl的值譯出SEML、CE0L、CElL,并輸出有效的地址和控制信號R WL、UBL、LBL、OEL到雙口RAM。接著是讀過程狀態(tài),為了得到有效的數(shù)據(jù),該過程未對輸入輸出操作。然后是讀過程等待狀態(tài),此時(shí),置LRDY信號有效且輸出有效的數(shù)據(jù)到PCI9052。最后是寫結(jié)束狀態(tài),在該過程的下一個(gè)周期將讀控制信號置為無效,狀態(tài)機(jī)恢復(fù)為讀空閑狀態(tài)。本文引用地址:http://www.104case.com/article/191746.htm

3 FPGA仿真實(shí)現(xiàn)

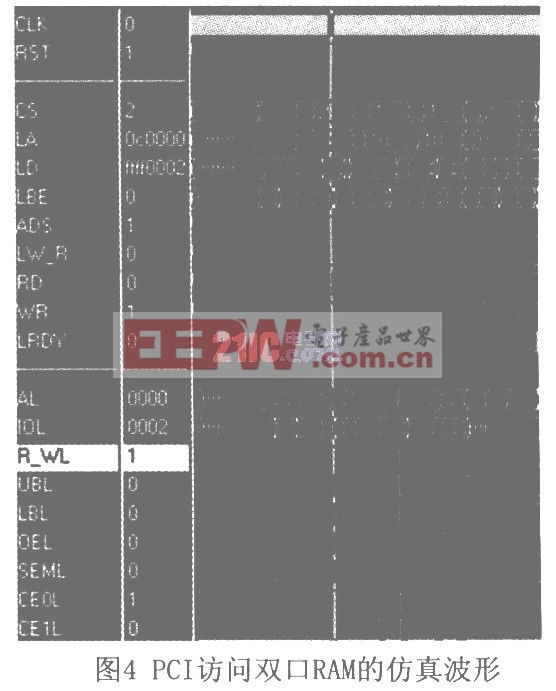

在Modelsim開發(fā)平臺下,實(shí)現(xiàn)了PCI9052讀寫雙口RAM的仿真過程,該仿真波形如圖4所示。從仿真波形可以看出該代碼可以實(shí)現(xiàn)將PCI90-52的讀寫控制信號轉(zhuǎn)換成雙口RAM的讀寫控制信號,完成時(shí)序的匹配。

4 結(jié)語

本設(shè)計(jì)采用了可編程邏輯芯片來實(shí)現(xiàn)PCI訪問雙口RAM的接口電路,該接口電路具有可改性與適用性。隨著微電子技術(shù)的發(fā)展,可編程器件的容量已經(jīng)達(dá)到千萬門級,越來越多過去必須由專用芯片或器件才能完成的工作現(xiàn)在都可以通過設(shè)計(jì)軟件由FPGA來實(shí)現(xiàn)了。硬件的軟件化已經(jīng)成為電子行業(yè)中不可阻擋的趨勢。

評論