基于FPGA的雙口RAM與PCI9O52接口設計

2 PCI和雙口RAM之間的接口設計

為了解決PCI9052和雙口RAM之間讀寫時序不匹配的問題,采用可編程邏輯器件CYCLONE-II來實現它們之間的接口電路,其信號連接關系如圖1所示。

PCI9052對雙口RAM發出讀寫指令需在FPGA配置完之后,這可以通過查詢CONF_DONE(和USERl相連)和INIT_DONE(和USER3相連)來確定FPGA是否配置完成。如采樣INIT_DONE信號,當其為高,表明FPGA配置完成;如采樣CONF_DONE,當其為高,則PCI9052還需要等待tCD2UM(min=18 μs,max=40 μs)時間后,才能對雙口RAM進行讀寫操作雙口RAM使用的是IDT70V28L,它的存取時間大于20ns。PCI9052采用非復用、單周期讀/寫模式,工作于25MHz時鐘,PCI訪問存儲器是以32位位寬,每讀寫操作一次在Local Bus上都對應2次16位位寬的操作,為了防止相鄰二次交易的沖突,每次狀態機都是以檢測ADS信號有效開始一次讀寫訪問,且插入一個NXDA等待周期。具體讀寫操作實現過程如下。

2.1 PCI9052寫過程

寫過程是用狀態機加以描述,該狀態機有6個狀態,分別是寫空閑、寫開始、寫等待數據、寫過程、寫過程等待和寫結束。具體的狀態轉移圖如圖2所示。

當系統復位后,BTERM、M S被拉高,LHOLD、MODE拉低,寫控制信號無效,狀態機處于寫空閑狀態。

當狀態機處于寫空閑狀態時,在每次上升沿采樣到ADS有效和LW R為高電平,且訪問雙口RAM空間(CS0或CSl有效),狀態機就進入寫開始狀態。在寫開始狀態,狀態機等待未進行一定的操作。接著是寫等待數據狀態,此時根據片選信號CS0和CSl的值譯出SEML、CEOL、CElL,并輸出有效的地址和控制信號R WL、UBL、LBL到雙口RAM。接著是寫過程狀態,為了得到有效的數據,該過程未對輸入輸出操作。然后是寫過程等待狀態,此時,置LRDY信號有效且輸出有效的數據到雙口RAM。最后是寫結束狀態,將片選信號CEOI。、CElL、SEMI。置位無效,在該過程的下一個周期將其余的寫控制信號置為無效,狀態機恢復為寫空閑狀態。

2.2 PCI9052讀過程

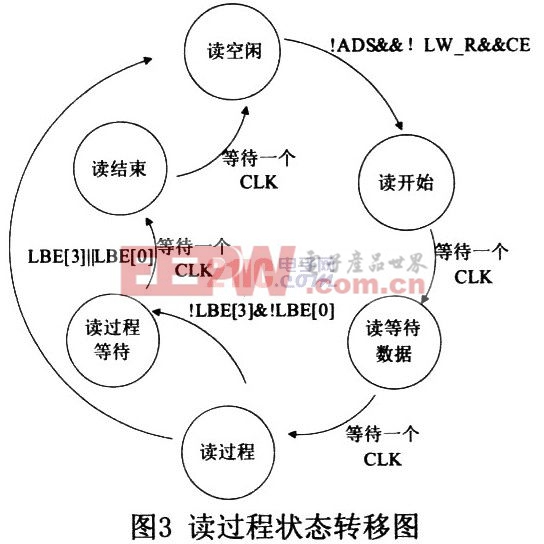

讀過程也是用狀態機加以描述,該狀態機有6個狀態,分別是讀空閑、讀開始、讀等待數據、讀過程、讀過程等待和讀結束。其狀態轉移如圖3所示。

當系統復位后,BTERM、M S被拉高,LHOLD、MODE拉低,讀控制信號無效,狀態機處于寫空閑狀態。

評論