印刷電路板如何疊層

3、選擇走線尺寸

把走線盡量擠在一起可以增加電路密度。非常密集的設計只需要較少的電路板層。既然印刷電路板費用與層的數目和板子的表面面積成正比,所以我們總是希望能夠使用最少的層數來達到這個目的。

走線越細,間隔越近,產生的串擾就越多,所能輸送的功率也就越小,這種在串擾、走線密度和功率之間的權衡,對低成本的產品設計非常關鍵。

讓我們首先來處理功率輸送能力的問題,因為這個約束條件最簡單。

印刷電路走線的功率輸送能力主要取決于它的橫截面面積和容許的上升溫度。對于一個給定的橫截面面積,一條走線上高于環境的溫度的粗略地與它耗散的功率成正比。升溫在高是不可靠的,而且會使附近的數字電路變熱。在數字產品中,保守的走線加熱上限是10℃。

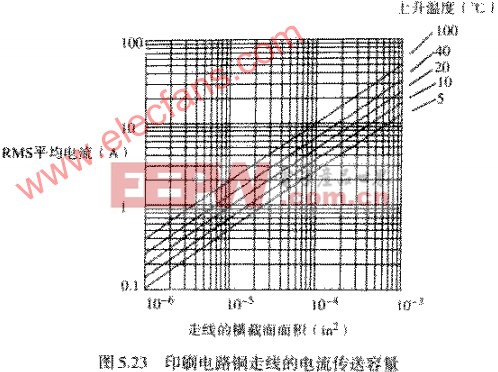

圖5.23描述了最大的功率輸送能力和溫度上升的關系。在圖5.23中,水平軸顯示的是橫截面面積,單位為IN的2次方,縱軸顯示的是該線在給定升溫值時的允許電流。

舉例來說,一個0.010IN寬的1OZ的銅走線(0.001 35IN厚),在溫度升高10℃的情況下,可以安全地通過750MA的電流。

除了大的電源分配總線,功率很少成為一個重要的約束條件,隨著薄膜技術的廣泛使用,由于其走線的橫截面面積非常小,布線的加熱限制可能變得更普遍。

走線寬度上的第二個不太重要的限制來自生產制造過程。表5.1列出了在各種不同的生產過程中可達到的最小走線寬度。

對于任何生產過程,當線寬接近可達到的最小走線寬度時,生產量將會降低,而且費用將會上升,這個因素將阻止大多數的設計者使用可達到的最小線寬。

其他一些因素會使走線寬度增加,腐蝕程序控制得不好,會造成線寬的變化比較大。在小線寬時,線寬變化的百分比決定著阻抗容限的百分比,有時這種變化可能是無法接受的,要想精確控制阻抗,可能需要使用比可達到的最小走線寬度字貢得多的線。

對于功率,費用和阻抗容限的考慮通常促使選擇特定的線寬。給于給定的線寬,阻抗約束決定層高。

然后使用關于串擾的公式,參見式![]() ,算出相鄰走線間隔的最小值,這個值稱為最小走線間距。在走線之間的未用距離稱為走線間隔。走線間隔加上線寬等于走線間距。

,算出相鄰走線間隔的最小值,這個值稱為最小走線間距。在走線之間的未用距離稱為走線間隔。走線間隔加上線寬等于走線間距。

評論