基于FPGA的LDPC編碼設計

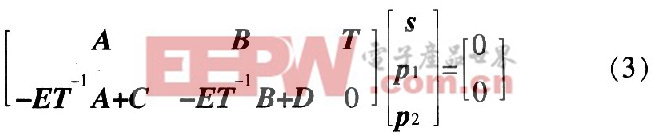

設c:[sp1 p2],其中s為系統信息部分,p1和p2共同組成校驗信息部分,p1長為g,p2長為(m-g)。HcT=0左乘

得到

得到

定義F=-ET-1 B+D,并且假定F是非奇的,由式(3)可得到p1和p2的求解式分別為

在式(4)求解p1的過程中,要求矩陣F可逆,因此F必須為非奇異的,即可逆。因此實際編碼前必須進行秩校驗。為得到F,對原始H矩陣進行高斯消元得到式(6)的形式:

如果F為奇異的,則將F中的列與其最左邊的列進行交換,直到F非奇異為止。

編碼復雜度主要由g×g維矩陣F-1與向量(-ET-1 A+C)sT相乘決定。RU算法在g很小時,即g2n時,編碼復雜度與碼長n成線性關系。因此,為了進行有效編碼,預處理要使得g應盡量的小。

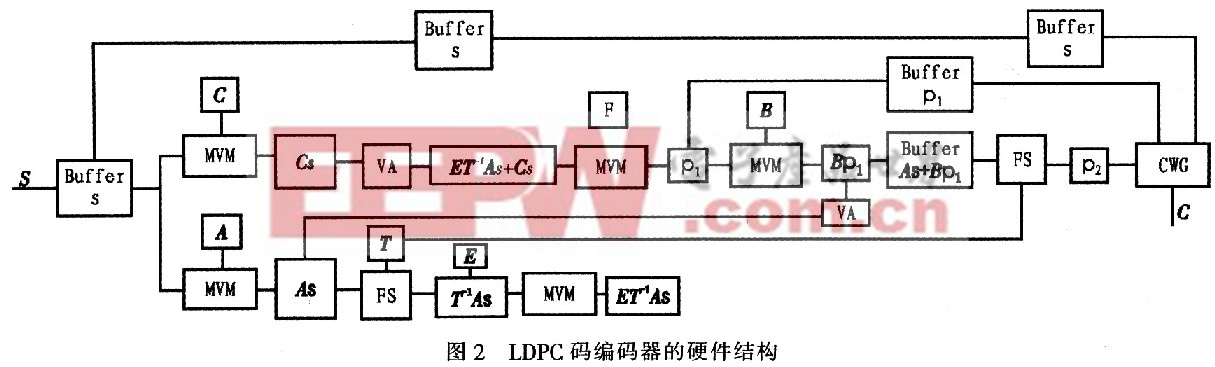

2.2 編碼器硬件結構

基于RU算法的LDPC編碼實現過程主要是計算p1、p2的過程。設計編碼器時,為了提高編碼速度,將可以同時計算的步驟作并行處理,得到編碼器的硬件結構如圖2所示。本文引用地址:http://www.104case.com/article/191682.htm

圖2中,A、B、C、E分別代表圖1中相應的矩陣,其中,F=-ET-1 B+D。從圖2可知LDPC編碼器主要由矩陣向量相乘(MVM)、前向迭代(FS)、向量相加(VA)和向量合成器(CWG)等運算單元以及存儲各個矩陣相關信息的存儲器組成。因為前向迭代運算基本上是矩陣與向量的乘法計算,所以矩陣向量乘法是LDPC編碼過程最核心的單元。

3 矩陣向量乘法器(MVM)的實現

矩陣與矩陣的乘法運算以及前向迭代運算實質上都是矩陣與向量的乘法。下面說明矩陣向量乘法器硬件實現。

對于LDPC編碼器,如何有效存儲各個矩陣的信息是降低復雜度的關鍵。本文采用存儲矩陣中元素‘1’在行中的位置以及對應行行重,如表1所示。例如矩陣X第3行的“1”元素,在行中的位置分別為“0”、“4”,該行的行重為2。由于LDPC編碼過程中使用的矩陣大多是稀疏矩陣,所以采用該矩陣存儲方案能比較有效地利用存儲的空間并有利于矩陣與向量乘法的快速實現。

評論