基于流水線技術的并行高效FIR濾波器設計

4 FIR濾波器的電路設計與仿真結果

在數字濾波器設計時,首先根據濾波器的頻率特性,選定濾波器的長度和每一節的系數。就目前的設計手段而言,對節數和系數的計算可以采用等波動REMEZ逼近算法編程計算。但是,目前最好的方法還是使用使用的EDA軟件來完成。在選擇了設計方法和設計要求后,計算出各節系數,并以圖形的直觀形式顯示幅頻、相頻、沖激響應和零極點圖。

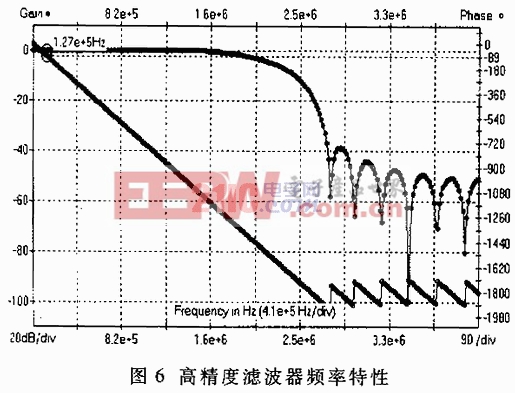

圖6是一個采用等波動設計方法生成的均方根升余弦(RRC)FIR濾波器的頻域特性。其中,滾降系數為0.35,輸入數據率是2.048MHz。

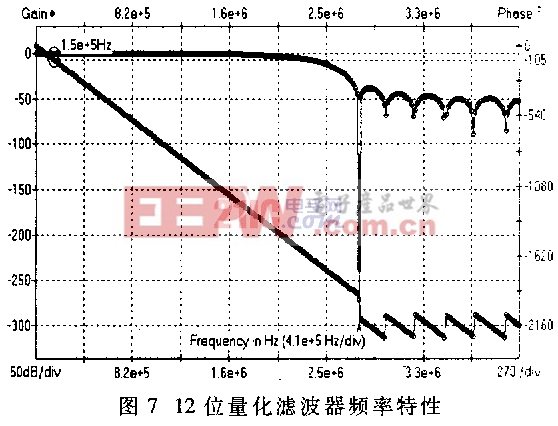

由于在數字濾波器中,各節系數字長有限,所以還要對計算出來的實系數進行量化處理,即浮點數向定點數轉換。系數量化后的頻域特性如圖7所示,量化字長為12。

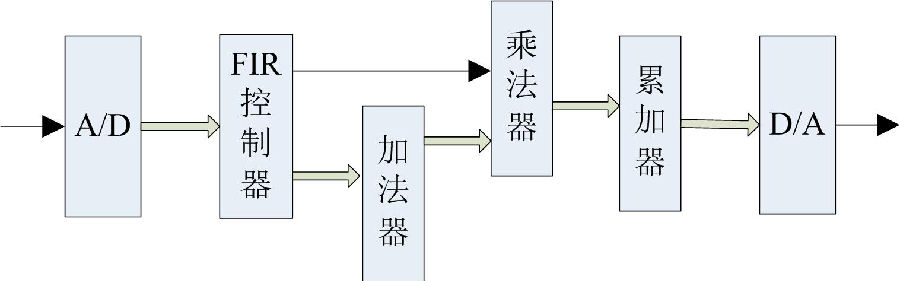

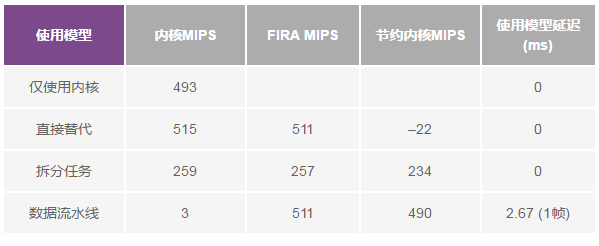

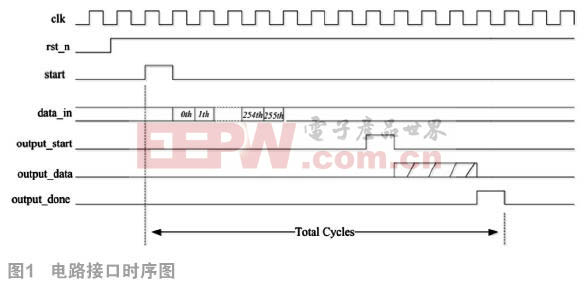

筆者采用流水線技術,根據得到的濾波器系數用VHDL語言編寫了濾波器程序。為了充分利用FPGA中四輸入查找表的電路結構,一般采用每8節為濾波器的一個基本單元。設計中通過采用流水線技術提高速度,對于更多階數濾波器的設計,可以采用擴展的方法來實現。仿真結果如圖8所示。

評論