基于流水線技術的并行高效FIR濾波器設計

在并行濾波器的設計中,每一個乘法器的一端輸入數據,另一端為固定常數。對于常數乘法器,可以預先將常數的部分乘積結構存儲起來,然后通過查表的方式實現兩個數據的乘積。以16位輸入、常數為14位的乘法器為例,給出其實現結構如圖2所示。

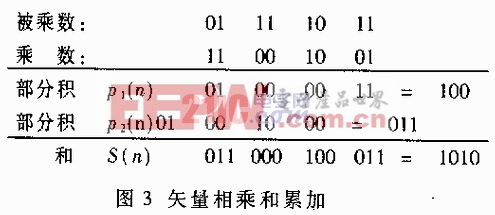

對于無符號數來說,這是一種理想結構。但是在實際使用中,通常使用有符號數且常用補碼的形式,因此需要對這種結構進行改進。一種改進方法是將輸入的數據分開,即最高的幾位作為有符號數處理,其它作為無符號數處理。第二種改進方法是將符號數經過補碼/原碼變換器變換成原碼,然后,將原碼作為無符號數處理,通過有符號數的符號位來控制加法器的加減。第三種改進方法是一種優化方法,即要用三個二進制補碼變換器,處理輸入的有符號數和濾波器的系數,這樣可以避免使用有符號數的乘法和加法運算。具體的乘法累加器運算過程及結果如圖3所示。其中,對應乘數高位和低位部分積p1(n)和p2(2)可以分別先垂直相加后水平相加,或者先水平相加后垂直相加,最后的結果是一樣的。若采用后種方法,由于FIR濾波器的h(n)均為常數,得到部分積的矢量乘法運算就演變成了查表法,其中,S1(n)表示S(n)的最低有效,p1表示最低有效位部分積之和。

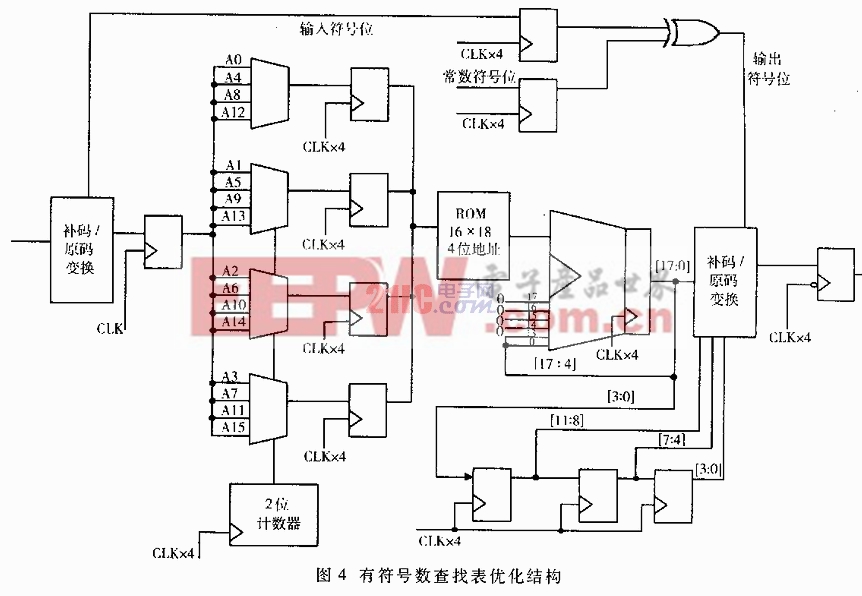

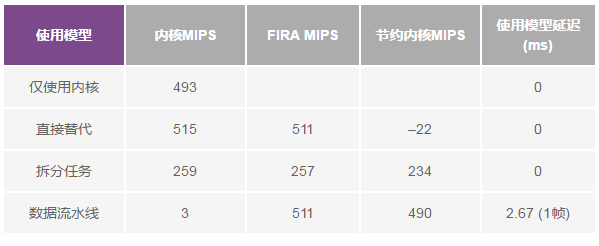

同理,得p2,將p2左移一位與p1相加,便得到最后結果。這種查表法就是采用流水線技術進行FIR濾波器算法分解的基礎,當字長增加時,相應得到p3、p4等。并相應移位相加即可。 在這種結構中,時鐘是f1,內部操作的時鐘是4×f1,其中的4個多路復用器每次可以從16路信號中選出4位用作ROM的地址線。每次4位地址從ROM中讀出數據,經過相應的移位相加即可,兩位計數器用來控制這些多路復位器的輸出。 比較圖6與圖7,不難看出,系數在量化前后的頻域特性是不同的,量化帶來了頻域特性的惡化。在驗證了量化后的頻域特性滿足設計要求和系數的有效性之后,就可以進行FPGA電路的設計。 本文介紹了并行高效數字濾波器的設計方法,給出了電路的仿真結果。利用VHDL語言,采用可重復配置的FPGA,降低了設計成本,提高了系統的適用性。由于FIR濾波器的系數是常數,可以保存在ROM中,在運算的通過查找表的方法可很快得到乘法輸出,減少了使用的資源和布線延時,節省了運算時間。在設計中,充分利用先進的EDA團體操,大大提高了設計效率。

采用流水線技術和加法器的資源共享技術可以更好地提高常數乘法器的優越性。16比特輸入、14比特常數的這種方法的常數乘法器的結構如圖4所示。

3 FIR濾波器的FPGA實現

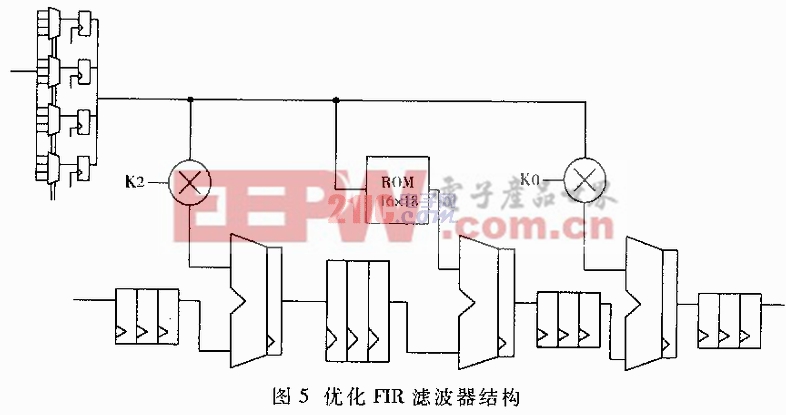

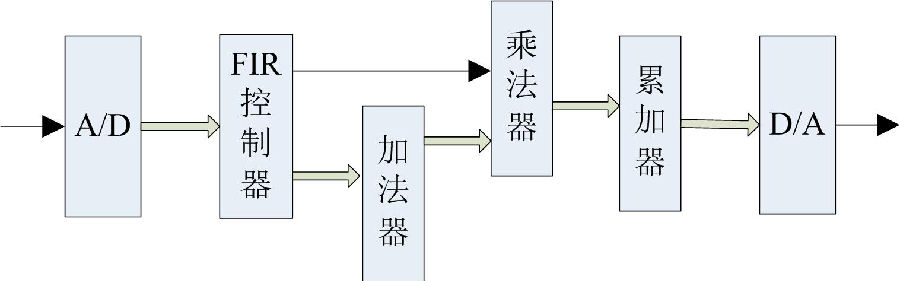

按照第2節所描述的第三種優化方法實現常數乘法器,乘法器輸出以后按照圖4所示的濾波器結構,通過流水線技術的加法器可以實現高效的濾波器。值得注意的是:在乘法器輸出的時候需要對輸出的數據進行一位擴展,可以避免加法器的溢出問題。

為了有效地利用資源,先通過多路復用器將輸入的序列復選出來,這樣所有常數乘法器可以共用一個多路復用器,然后通過ROM查表方法實現常數乘法器。優化后的原理結構如5所示。

評論