基于FPGA的IRIG-B(DC)碼產生電路設計

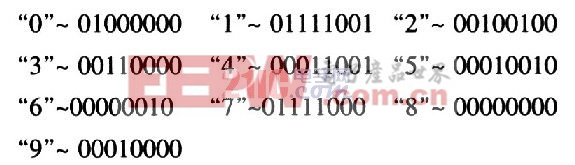

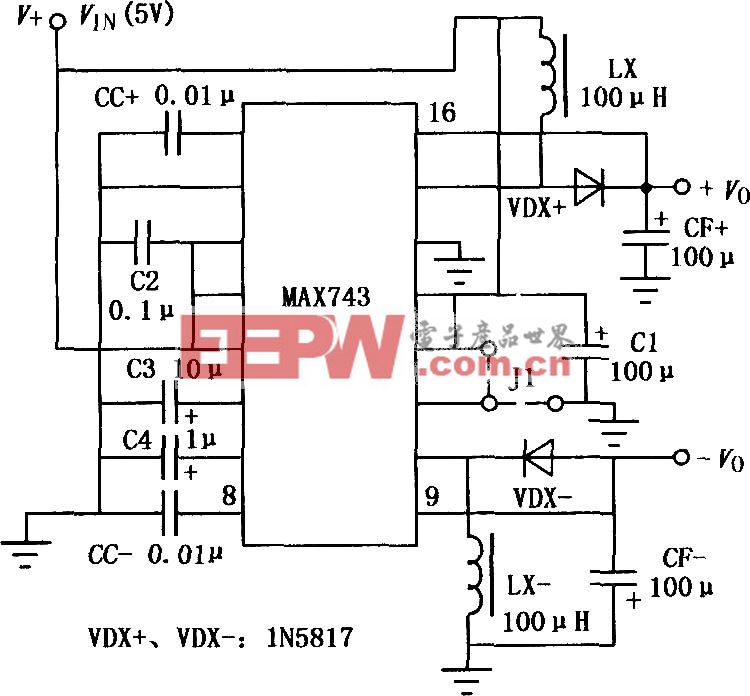

選擇EPlC6T144的37引腳作為異步串行輸出引腳,與MAX3232E的lO引腳(T2IN)連接,將從FPGA出來的TTL電平轉換為串行輸出電平從7引腳(T20UT)輸出,串行電平轉換器采用MAX3232E。選擇EPlC6T144的4l、42引腳作為2路IRIG-B碼信號輸出,因為IRIG-B(DC)碼采用RS422電平輸出,而從EPIC6T144的4l、42引腳輸出脈沖是TTL電平,所以必須進行電平轉換,本設計采用TI公司的AN26LS31CD差分驅動器。采用8段數碼管作為時間顯示器件,顯示的信息有天、時、分和秒,共需9個器件,每個8段數碼管的0~9個數字顯示邏輯為:

本文引用地址:http://www.104case.com/article/191635.htm

本文引用地址:http://www.104case.com/article/191635.htm3 系統軟件程序設計

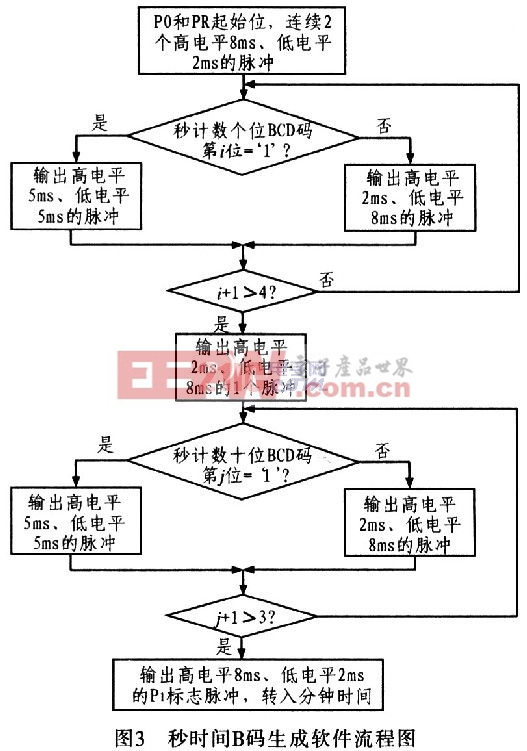

使用VHDL硬件描述語言進行編程,編譯環境采用Altera公司的QuartusII7.1。根據圖1所示B碼脈沖序列寬度圖譜,以秒的B碼串產生為例。說明VHDL編程設計過程,流程圖如圖3所示。分、時和天的軟件設計根據圖l所示的B碼示意圖,參考秒的設計流程來設計,將100個碼元對應的脈沖串按照圖l的脈沖寬度輸出,就形成整個一幀IRIG-B(DC)碼的脈沖串。

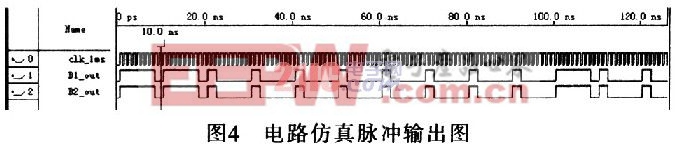

4 電路仿真

電路仿真脈沖輸出如圖4所示,圖中Bl_out和B2_out是IRIG-B(DC)碼的輸出脈沖,clk_lms是根據晶體振蕩器輸入脈沖而產生的模擬l ms信號脈沖,可以看出,當連續8個elk_1ms的脈沖時,Bl_out和B2_out保持高電平,即保持了8 ms的高電平,后面的脈沖都嚴格的遵守圖l所示的IRIG-B(DC)碼的規則。

5 結論

通過仿真和實際使用表明,該設計電路所產生的IRIG-B(DC)時間碼穩定、連續、準確,電路板功耗低、成本低,操作靈活簡單,在測控領域有廣闊的應用前景。

評論