基于FPGA的快速9/7整形離散小波變換系統(tǒng)設(shè)計

3 仿真與綜合

為了驗證本文設(shè)計系統(tǒng)的性能,使用Modlesim6.3仿真軟件對系統(tǒng)進(jìn)行了仿真測試,下面是采用大小為1 024×1 024,圖像數(shù)據(jù)為8位的測試圖像進(jìn)行測試仿真的部分波形圖。

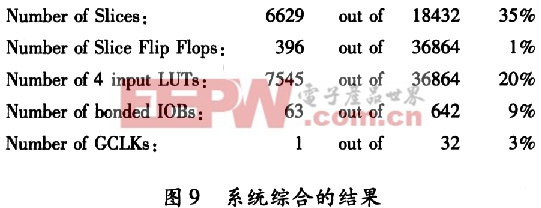

在Xilinx提供的ISE7.1仿真軟件下搭建測試平臺,對設(shè)計系統(tǒng)進(jìn)行綜合,結(jié)果如圖9所示。

設(shè)計系統(tǒng)時鐘頻率可達(dá)到54 MHz,滿足對圖像數(shù)據(jù)的實時處理要求。

4 結(jié)束語

本文主要討論了基于FPGA的快速9/7整形離散小波變換系統(tǒng)設(shè)計,該結(jié)構(gòu)采用內(nèi)部RAM的循環(huán)覆蓋的存儲方式,使對存儲器的需求量減小,從而減小了硬件功耗,同時采用基于行的列變換方式,提高了的系統(tǒng)運行,可實現(xiàn)對遙感傳輸圖像的快速實時處理。

p2p機(jī)相關(guān)文章:p2p原理

評論