SDH中E1接口數字分接復用器的VHDL設計及FPGA實現

摘要:介紹了SDH系統中的接口電路――數字分接復用器的VHDL設計及FPGA實現。該分接復用器電路用純數字同步方式實現,可完成SDH系統接口電路中7路(可擴展為N路)E1數據流的分接和復用。該設計顯示了用高級硬件描述語言VHDL及狀態轉移圖作為輸入法的新型電路設計方法的優越性。

關鍵詞:分接復用器 狀態轉移圖 VHDL FPGA

為擴大數字通信系統的傳輸容量,信道上的信號都是在發送端分接,在接收端復接。在通信接口電路中能完成這一功能的電路就叫作分接復用器。

該分接復用器提供了標準的E1接口可供SDH系統方便使用。在點到點通信時,采用該分接復用器可以使系統速率提高到N(N為1、2、3等)倍E1速率以上。當用戶需求速率超過E1速率但又達不到34.368Mbps的VC-3速率時,一個好的方法就是采用E1分接復用器接口電路。比如以太網通信需要10Mbps的速率時,采用該分接復用器,取N=7就可實現通信要求。

針對目前國內SDH系統中還沒有一個專門的E1分接復用芯征,本文介紹一種用高級硬件描述語言VHDL及狀態轉移圖完成該發接復用器的設計的新型設計方法及其FPGA實現。并給出了用Xilinx Foundation tools EDA軟件設計的電路仿真波形及Spartan XCS30XL完成FPGA實現的結果。

1 數字分接復用器結構原理

本數字分接復用器的功能是:在發送端把12Mbps經過編碼的有幀結構的Ethernet(以太網)碼流分接為7路標準E1接口速率數據流,SDH設備再把這7路數據映射到155Mbps的速率去通過光纖傳輸到下一個SDH設備;在接收端由SDH設備從155Mbps的數據流中取出7路標準E1速率數據正確恢復為原來的12Mbps的Ethernet(以太網)碼流。

發送端12Mbps有幀結構數據幀間由全1空閑碼填充。從數字分接復用器發送輸出的7路E1數據由于傳輸處理過程中路中不同,必然會造成7路E1數據在傳輸過中的各路時延不一致,這就使得各路數據不同步。在設計中如何在接收端使得7路E1數據同步,從而正確恢復原發送端12Mbps數據就成了一個難題。針對這一問題制定出了如下的解決方案。

1.1 數字分接器原理框圖及說明

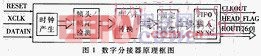

如圖1所示,把數字分接器從總體上劃分為:時鐘產生、幀頭/幀尾檢測、串并變換、固定插零、FIFO插入SYNC五個模塊。

在發送端,分接器的時鐘產生電路把14Mbps系統時鐘XCLK轉變為12Mbps時鐘,用這一時鐘對端口來的12Mbps成幀數據DATAIM做幀頭(1100010001)/幀尾(1000000001)檢測,檢測出幀頭后再做串/并變換操作,這樣就初步完成了分接器的功能。但是,為了使數字復接器能正確復接就需要在分接器輸出的7路數據中分別插入同步頭SYNC(0111111110)。為了使數據和插入的SYNC區別開來,須要在7路數據中每隔7bit就固定地插入“0”。這樣,就保證了插入的SYNC不會與正常的掌握相混淆,從而也使得分接出的7路數據變為標準的E1數據。

1.2 數字復接器原理框圖及說明

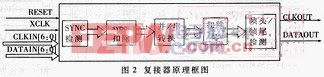

數字復接器原理框圖如圖2所示。與分接器相呼應,可把復接器從總體上劃分為:SYNC檢測、SYNC扣除、并/串轉換、扣除零、幀頭/幀尾檢測5個模塊。

評論