基于FPGA的動態可重構系統設計與實現

0 引 言

由于數字邏輯系統功能復雜化的需求,單片系統的芯片正朝著超大規模、高密度的方向發展。對于一個大規模的數字系統而言,系統規模是基于各種邏輯功能模塊的組合。但是,無論是時序邏輯系統,還是組合邏輯系統,或者組合/時序混合系統,從時間軸上來看,系統中的各個功能模塊并不是時刻都在工作,而是根據系統外部的整體要求,輪流或循環地被激活或工作。并且,隨著數字邏輯規模的擴大,在相同速度條件下,在一定的時間區間,其功能模塊的平均使用率將下降。因此,系統設計應該從傳統追求大規模、高密度的方向,轉向如何提高資源利用率,用有限的資源實現更大規模的邏輯設計上來。可重構計算技術能夠提供硬件的效率和軟件的可編程性,它綜合了微處理器和ASIC的特點,在空間維和時間維上均可變。

1 可重構技術概述

1.1 可重構的定義

可重構就是在電子系統的工作狀態下,動態地改變電路的結構。這主要通過對系統中的可編程邏輯器件進行重新配置或者局部重新配置來完成。利用可重構技術,能在只增加少量硬件資源的情況下,使系統同時具有軟件實現和硬件實現的優點。

1.2 可重構方式的分類

按照重構的方式,系統重構可以分為靜態系統重構(Static Reconfiguration)和動態系統重構(Dynamic Reconfiguration)。

1.2.1 靜態系統重構

靜態系統重構是指目標系統的邏輯功能靜態重載,只能在運行前配置的系統,如圖1所示。

FPGA功能在外部邏輯的控制下,通過存儲于存儲器中不同的目標系統數據重新下載,從而實現芯片邏輯功能的改變。

1.2.2 動態系統重構

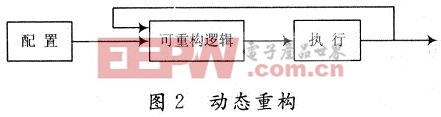

動態系統重構是指能在運行過程中實時配置的可重構系統,如圖2所示。

對于時序變化的數字邏輯系統,其時序邏輯的發生不是通過調用芯片內不同區域、不同邏輯資源組合而成的,而是通過對具有專門緩存邏輯資源的FPGA進行局部或全局的芯片邏輯的動態重構而快速實現的。動態系統結構的FPGA具有緩存邏輯(Cache Logic),在外部邏輯的控制下,通過緩存邏輯對芯片邏輯進行全局或局部的快速修改,通過有控制重新布局布線的資源配置來加速實現系統的動態重構。就動態重構實現面積的不同,又可以分為全局重構和局部重構。

評論