基于模塊化設計方法實現FPGA動態部分重構

按照模塊化設計流程,分別對固定模塊fix和可重構模塊reconfig_a和reconfig_b進行設計綜合,再將兩個可重構模塊分別和固定模塊進行組合,完成整體設計。此過程中可重構模塊和FPGA的整個設計分別生成配置比特流。

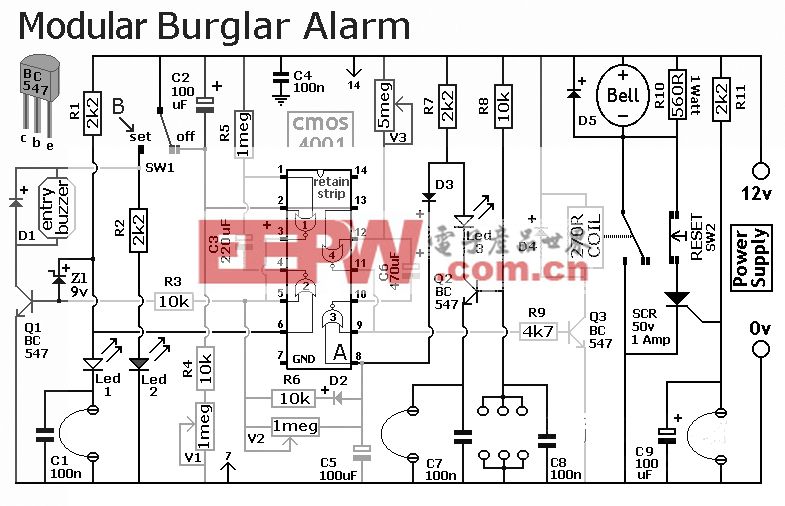

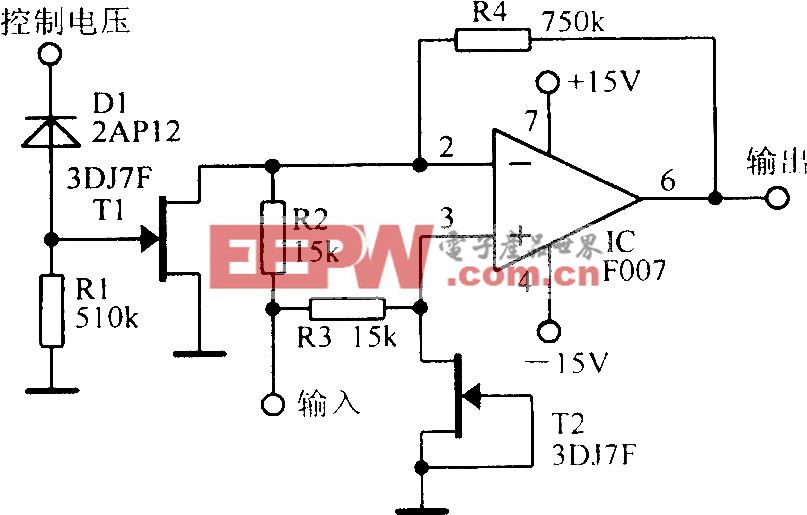

圖3和圖4是FPGA部分重構前后的整個設計的物理實現,圖中左半部分為固定模塊區域,右半部分為可重構模塊區域。從兩圖中可知在部分重構前后可重構模塊區域內布線發生變化,而固定模塊區域內布線沒有發生變化。

圖3 fix和reconfig_a整體設計的物理實現結果

圖4 fix和reconfig_b整體設計的物理實現結果

FPGA動態部分重構時首先須將整個配置文件下載到器件中,重構時系統根據運行的需要選擇適合的部分重構配置比特流。Virtex-E XCV600E配置比特流的大小為495204個字節,而可重構模塊reconfig_a和reconfig_b配置比特流的大小分別為93324個字節和111868個字節,因此采用部分重構不僅能夠在運行不間斷的情況下更新可重構模塊區域內的邏輯功能,而且也能使重構配置時間大大減少。

3 結論

本文以Xilinx FPGA為研究對象,介紹了采用模塊化設計實現FPGA動態部分重構功能的方法。FPGA的動態部分重構功能使硬件設計更加靈活,可以將不同設計定位到芯片內同一邏輯資源部分,重構此部分邏輯資源,同時保持其他部分電路功能正常,從而靈活快速的改變系統設計,能夠減少器件的花費,降低功耗、更有效的利用電路板空間,可以應用于系統實時容錯、自適應硬件算法等。

本文作者創新點:基于FPGA動態可重構技術將設計從一個純空間的數字邏輯系統轉換為在時間、空間混合構建的數字邏輯系統。這種技術是數字系統設計方法、設計思想的變革,使FPGA資源利用率成倍提高。目前我國在FPGA可重構技術方面開展的研究很少。本論文闡述了采用模塊化設計實現FPGA動態部分重構的方法,能夠使FPGA部分邏輯功能重新配置過程中,其余部分邏輯功能正常運行,即實現了FPGA邏輯功能的動態部分重構

評論