基于模塊化設(shè)計方法實現(xiàn)FPGA動態(tài)部分重構(gòu)

關(guān)鍵詞:FPGA;動態(tài)部分重構(gòu);重構(gòu);Virtex

隨著可編程技術(shù)的不斷發(fā)展,F(xiàn)PGA被廣泛應(yīng)用于電子設(shè)計的各個領(lǐng)域。新的設(shè)計思想和設(shè)計方法也被不斷的提出和應(yīng)用,如FPGA的動態(tài)部分重構(gòu)技術(shù)。所謂動態(tài)重構(gòu)是指對于時序變化的數(shù)字邏輯系統(tǒng),其時序邏輯的發(fā)生,不是通過調(diào)用芯片內(nèi)不同區(qū)域不同邏輯資源的組合來實現(xiàn),而是通過對具有專門緩存邏輯資源的FPGA,進(jìn)行局部和全局芯片邏輯的動態(tài)重構(gòu)而快速實現(xiàn)。動態(tài)可重構(gòu)FPGA器件在編程結(jié)構(gòu)上應(yīng)具有專門的特征,其內(nèi)部邏輯塊和內(nèi)連線的改變可以通過讀取不同的配置比特流文件來實現(xiàn)邏輯重建。動態(tài)部分重構(gòu)是指重新配置FPGA的部分區(qū)域,重構(gòu)過程中,F(xiàn)PGA其余部分的工作狀態(tài)不受影響。此方式減小了重構(gòu)范圍和單元數(shù)目,從而大大縮短了FPGA的重構(gòu)時間。

本文引用地址:http://www.104case.com/article/191607.htm應(yīng)用FPGA動態(tài)部分重構(gòu)功能使硬件設(shè)計更加靈活,可用于硬件的遠(yuǎn)程升級、系統(tǒng)容錯和演化硬件以及通信平臺設(shè)計[1]等。動態(tài)部分重構(gòu)可以通過兩種方法實現(xiàn):基于模塊化設(shè)計方法(Module-Based Partial Reconfiguration)和基于差別的設(shè)計方法(Difference-Based Partial Reconfiguration),本文以基于模塊化設(shè)計為例說明實現(xiàn)部分重構(gòu)的方法。

1 FPGA配置原理簡介

本文針對Xilinx公司的FPGA進(jìn)行研究,支持模塊化動態(tài)部分重構(gòu)的器件族有Virtex/-II/-E和Virtex-II Pro。

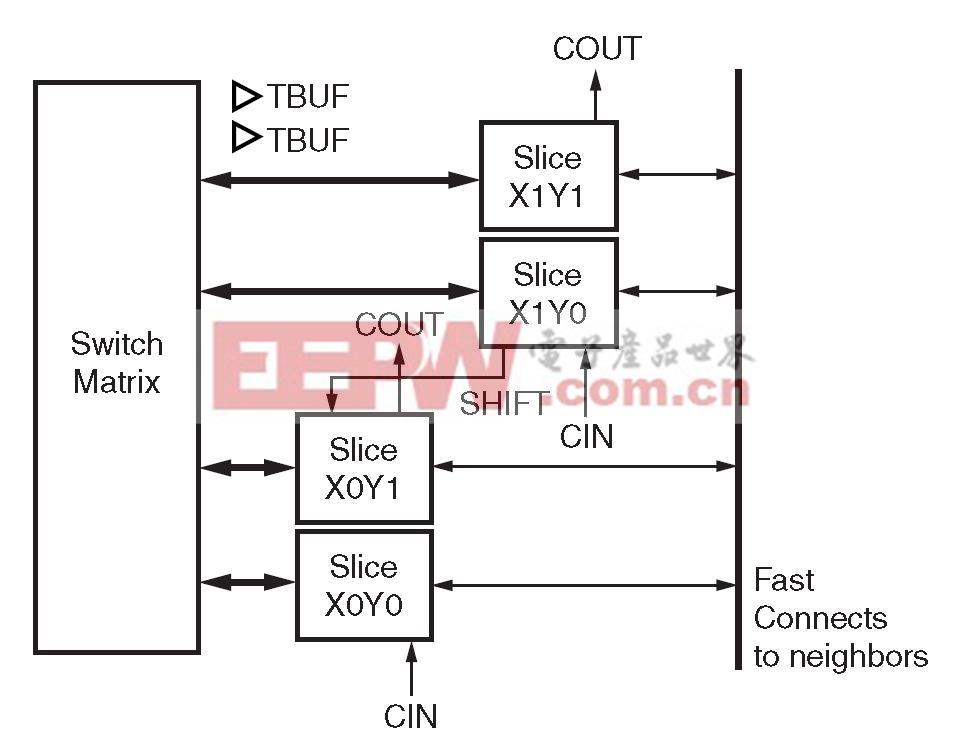

Xilinx公司FPGA是基于SRAM工藝的,包括配置邏輯塊(CLBs),輸入輸出塊(IOBs),塊RAMs,時鐘資源和編程布線等資源[2]。CLBs是構(gòu)造用戶所需邏輯的功能單元,IOBs提供封裝引腿與內(nèi)部信號引線的接口。可編程互連資源提供布線通道連接可配置元件的輸入和輸出到相應(yīng)的網(wǎng)絡(luò)。

存儲在內(nèi)部配置存儲器單元中的數(shù)值決定了FPGA實現(xiàn)的邏輯功能和互接方式。Virtex FPGA的配置存儲器是由配置列(Configuration Columns)組成的,這些配置列以垂直陣列的方式排列,如圖1給出了Virtex-E XCV600E器件的配置列構(gòu)成圖。配置存儲器可分為五種配置列:Center 列包含四個全局時鐘的配置信息;兩個IOB 列存儲位于器件左邊和右邊所有IOBs的配置信息;CLB列存儲FPGA基本邏輯功能的配置信息;Block SelectRAM Content列存儲內(nèi)部塊RAM的配置信息;Block SelectRAM Interconnect列存儲內(nèi)部塊RAM間互聯(lián)的配置信息[3]。

圖1 Virtex-E XCV600E的配置列構(gòu)成及地址

評論