基于FPGA的OPB_AHB總線橋接器的設計

實現兩種總線的互聯,關鍵是完成控制信號之間的轉換以及數據和地址的傳輸,本設計采用的方法包括。

(1)流水線方式, (2)將所有輸入的控制信號和數據地址總線都寄存一拍。

(3)控制信號都采用同 (4)步設計方法, (5)在OPB_Clk的上升沿觸發。

(6)數據的讀寫操作為同 (7)步讀寫。

4.1OPB2AHB_Brg的實現

(1) 所有控制信號采用同步設計思想,在 SOPB_Clk的上升沿觸發。 SOPB_Rst高電平有效,為同步復位,當其有效時,所有信號輸出 0狀態。

(2) 當橋接器檢測到 SOPB_Sel信號有效時,即表明橋接器被選中,成為 OPB總線上的從設備,或者檢測到 AHB_Resp信號狀態為RETRY,此時 OPB2AHB_Brg作為AHB總線上的主設備向 AHB仲裁器發出請求總線信號 AHB_BusReq。

(3) 當OPB2AHB_Brg檢測到 AHB總線側的允許信號 AHB_Grants時,說明橋接器的請求得 到允許,此時當 AHB_Ready有效時,可以根據 SOPB_BE判斷傳輸數據的大小,決定 AHB_Size的狀態,當 SOPB_BE為1111時,AHB_Size為010(32bit),SOPB_BE為1100或0011時,AHB_Size為001(16bit),SOPB_BE為0001、0010、0100、1000時,AHB_Size為000(8bit)。

(4) 當SOPB_RNW為高電平時,為讀取數據,數據流向是從 AHB_Rdata到Sl_Dbus,當 SOPB_RNW為低電平時,為寫數據,數據流向從 SOPB_Dbus到AHB_Wdata。地址總線相連,即SOPB_Abus連接AHB_Addr。

(5)當一次數據傳輸完成后, (6)置位Sl_xferAck信號, (7) 讓其輸出一個時鐘周期的高脈沖。

4.2 AHB_OPB_Brg的實現

(1) 當橋接器檢測到 AHB_Sel信號有效時,即表明橋接器被選中,成為AHB總線上的從設備,此時AHB2OPB_Brg作為OPB總線上的主設備向 OPB仲裁器發出請求總線信號 M_req。

(2)當橋接器接收到 OPB仲裁器發出的允許信號 OPB_Mgrant信號時, (3)表明橋接器可以

開始工作,(4)這個信號會激勵 M_Sel信號有效, (5)根據 IP核 BK3721的功能特性, (6) M_BE總是輸出 1111,(7) M_SeqAddr和M_busLock輸出為0。

(3) 當AHB_Write為高電平時,為寫數據有效,此時 AHB主設備向從設備橋接器寫數據,同時橋接器作為 OPB總線上的主設備向選中的 OPB從設備寫數據,數據流向為 AHB_Wdata到 M_Dbus。當AHB_Write為低電平時,為讀數據有效,此時 AHB主設備從橋接器(作為 AHB總線上的從設備)讀取數據,同時橋接器作為 OPB總線的主設備從選中的 OPB從設備讀取數據,數據流向為OPB_DBus到AHB_RData。

(8)當數據傳輸指 (9)示信號OPB_xferAck被檢測有效時, (10) AHB_Ready信號輸出高電平有效信號, (11)表示數據傳輸結束。

5.OPB_AHB橋接器的驗證

5.1 OPB2AHB_Brg的驗證

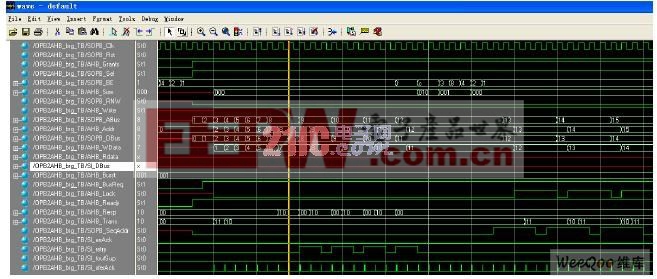

用verilog編寫testbench,在testbench中虛擬設備一個 AHB從設備存儲器 AHB_mem,存儲器的數據位寬和地址位寬都是 32位,通過測試平臺可以對虛擬存儲器進行數據的讀寫,并將數據的讀寫結果保存到 Wdata.txt文件中。

利用ModelSim工具對測試平臺進行仿真。在主設備向虛擬從設備寫數據時, SOPB_RNW為低電平,橋接器作為AHB上的主設備將 SOPB_DBus數據線上的數據通過 AHB_Wdata寫到 AHB_mem存儲器中,并在 WData.txt文件中顯示出來,仿真結果如圖 3 (a)所示。

圖3 (a) OPB2AHB_Brg寫數據仿真波形

評論