基于FPGA的三相函數信號發生器設計

2.4 波形選擇的實現

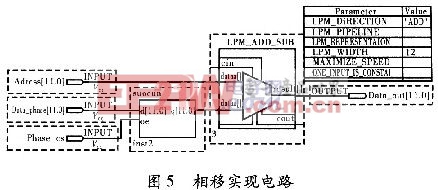

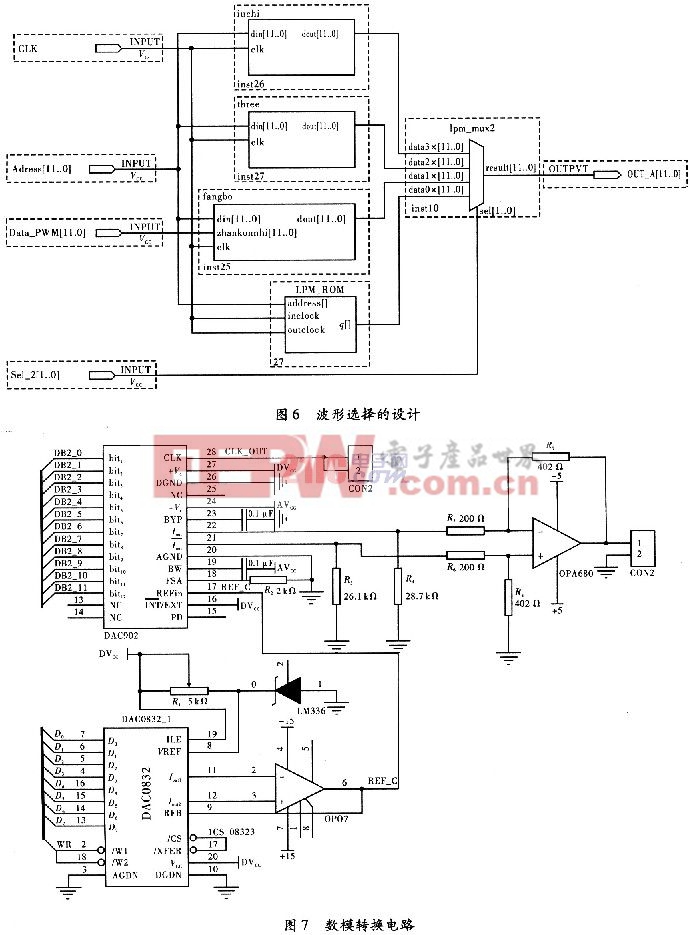

根據設計要求,每一相都可以實現正弦波、方波、三角波和鋸齒波任意一種波形的輸出,設計了一個4選1數據選擇器,控制端Sel[1.-.0]與單片機IO口相連,如圖6所示,以A相為例。本文引用地址:http://www.104case.com/article/191582.htm

2.5 幅度控制的實現

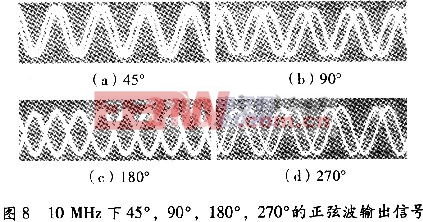

參考電壓可通過INT/EXT端選擇內部和外部。當該端口為高電平時選擇外部參考電壓,只要改變參考電壓,就可以改變輸出波形的幅值。DAC902外部參考電壓范圍0.10~1.25 V,因此只需采用8位D/A既可實現0.01 V的步進。如圖7所示,DAC0832輸出接到DAC902參考電壓輸入端REFin,通過單片機控制DAC0832輸出,進而控制DAC902參考電壓。

3 系統測試

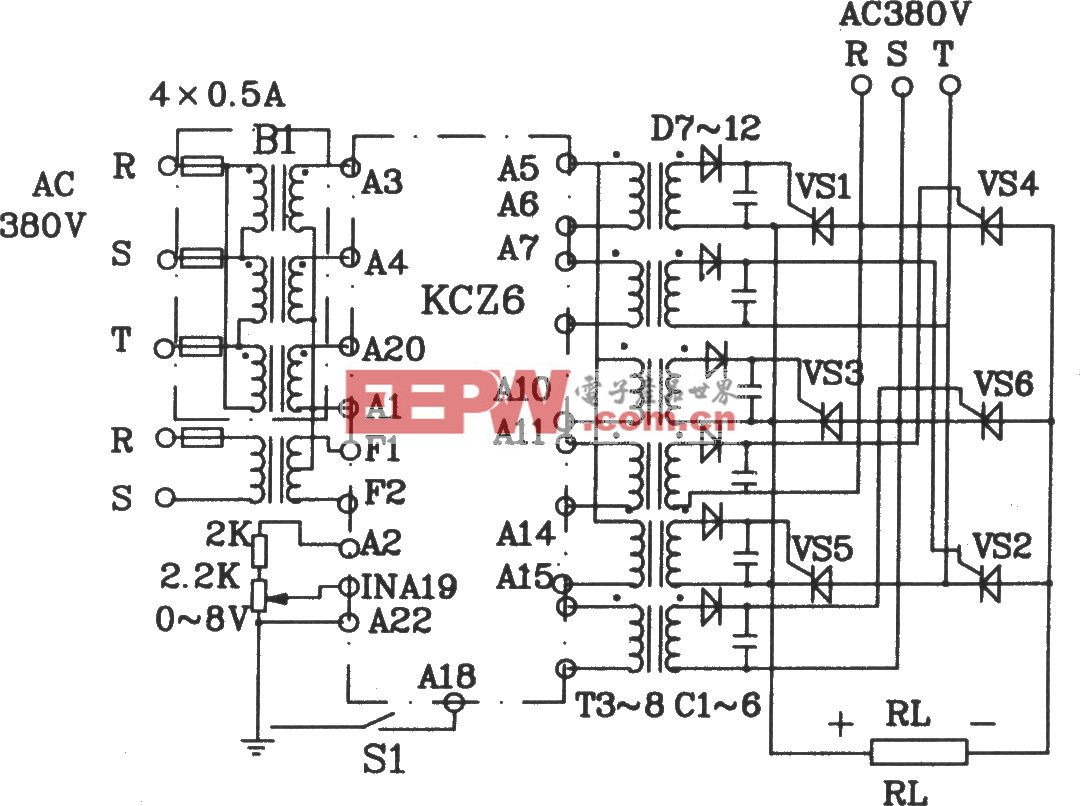

本系統波形參數設置通過觸摸屏輸入完成,用示波器測試50 Ω負載下的輸出波形,比較設置值與測試值之間的誤差,圖8為信號源輸出頻率為10 MHz,峰峰值為5 V,兩路信號相移分別為45°、90°、180°、270°時,在使用Fluck PM3394B 200 MHz Combiscope Instrument的“Analog”模式下,用數碼相機拍攝的正弦波的輸出波形。

經過多次測試和反復改進,最終實現了如下技術指標:

(1)輸出波形:正弦波、方波、三角波、鋸齒波。

(2)輸出波形頻率范圍:0.1 Hz~10 MHz。

(3)輸出頻率調節步長:0.01 Hz~10 kHz。

(4)輸出電壓范圍:10 mV~10 V(峰峰值)可調,幅度步進最小10 mV。

(5)方波占空比調節范圍:1%~99%。

由于示波器只有兩個通道,因此只能測量兩項信號之間的相位差。

在頻率穩定度方面,正弦波、三角波、方波和矩形波輸出波形穩定,這正是體現了DDS技術的特點,輸出頻率穩定度和晶振穩定度在同一數量級。由于采用了FPGA的內部時鐘,在倍頻分頻的結果后還是無法達到計算的時鐘,因此存在著誤差,但在頻率較高部分誤差稍明顯,因此設計中采用了軟件修正,從而減少了頻率較高部分的誤差。

對于波形幅度的控制上,由于波形在電路網絡存在一定的衰減,因此在程序中采用軟件補償進行修正。從測試結果可以看書軟件補償做得越細致誤差越小。

4 結束語

本項目以多功能、低功耗、操作方便、結構合理、易于調試為主要設計原則,在系統設計過程中,力求硬件線路簡單,充分發揮軟件編程方便靈活的特點,并最大限度挖掘FPGA片內資源,來滿足系統設計要求。

利用硬件描述語言VHDL編程,借助Ahera公司的Quartus II軟件環境下進行了編譯及仿真測試,在FPGA芯片上設計了函數發生器,產生正弦波、三角波、方波等多種波形,系統的頻率分辨率高,頻率切換速度比較快。設計采用了EDA技術,縮短了開發研制周期,提高了設計效率,而且使系統具有結構緊湊、設計靈活、實現簡單、性能穩定的特點。

評論