基于DDS和FPGA技術(shù)的高動(dòng)態(tài)擴(kuò)頻信號(hào)源的研究

在本文介紹的信號(hào)源中,載波頻率圍繞中心頻率10.7MHz做線性變化,線性變化的范圍Y和速率X由用戶從鍵盤輸入。軟件實(shí)現(xiàn)的方法是利用單片機(jī)的定時(shí)中斷,每500微秒計(jì)算一次頻率,并轉(zhuǎn)化為頻率控制字,寫入AD9854。為了提高精度,模擬連續(xù)變化,定時(shí)的時(shí)間越短越好。而單片機(jī)內(nèi)部計(jì)算的效率很低,因此為了減少中斷服務(wù)程序的計(jì)算量,可以在中斷開(kāi)始之前把一部分需要用到的參數(shù)先計(jì)算出來(lái):

載波頻率變化的步長(zhǎng): STEP=X×t=X×500μs

一個(gè)狀態(tài)內(nèi)的變化總次數(shù):TOTAL COUNT=Y/STEP=Y/(X×t)

步長(zhǎng)對(duì)應(yīng)的頻率轉(zhuǎn)換字:SFTW=STEP×248/REFCLOCK

計(jì)算出上述三個(gè)參數(shù)之后,在中斷服務(wù)子程序中只需設(shè)置一個(gè)計(jì)數(shù)器COUNT,根據(jù)所在的狀態(tài)(如圖2所示的0或1,2,3),用中心頻率的頻率轉(zhuǎn)換字CENTER FTW加上或者減去SFTW×COUNT,再送至AD9854中即可。

當(dāng)然,也可以將事先計(jì)算好的數(shù)據(jù)存儲(chǔ)起來(lái),再查表,減少中斷響應(yīng)時(shí)間,但是這樣存儲(chǔ)的數(shù)據(jù)量比較大:以X=2.0Hz/s,Y=40kHz,500μs中斷一次為例,就至少要存儲(chǔ)40M個(gè)數(shù)據(jù)。如果存儲(chǔ)的數(shù)據(jù)過(guò)少,所模擬的變化就不夠連續(xù)。因此,前述方案較好。

實(shí)際上,在載波變化的同時(shí),偽碼的頻率也應(yīng)該發(fā)生相應(yīng)的變化,變化的方法也是用單片機(jī)定時(shí)改變AD9850的頻率控制字,具體的軟件技術(shù)同AD9854,此處不再贅述。

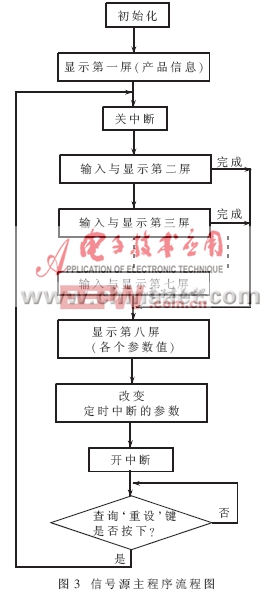

3 高動(dòng)態(tài)擴(kuò)頻仿真信號(hào)源的軟件流程

信號(hào)源主程序的流程如圖3所示。程序初始化包括對(duì)AD9850和AD9854的復(fù)位,設(shè)置AD9850和AD9854缺省值,設(shè)置數(shù)據(jù)和偽碼的組別初值。液晶顯示共有八個(gè)顯示畫面,第二屏至第七屏提示用戶輸入各個(gè)參數(shù)。需要設(shè)定的參數(shù)有:數(shù)據(jù)碼組、偽碼碼組、幀碼容錯(cuò)數(shù)、載波變化范圍、載波變化率、偽碼變化率、輸出幅度衰減方式等。然后單片機(jī)同時(shí)工作在中斷和查詢方式。如果查詢到‘重新設(shè)定’的鍵被按下,就禁止中斷,重新輸入?yún)?shù),再開(kāi)中斷模擬新的參數(shù)條件下的信號(hào)。

4 高動(dòng)態(tài)擴(kuò)頻仿真信號(hào)源的性能指標(biāo)

·體制: PCM-CDMA-BPSK;

·PCM數(shù)據(jù):碼率10.26/5.12kbps可選,幀長(zhǎng)32/16Byte可選,幀碼容錯(cuò)由面板手動(dòng)加;

·信道編碼: 維特比編碼 K=7, r=1/2;

·擴(kuò)頻調(diào)制:偽碼率:5.23264MHz,偽碼長(zhǎng)255/511可選;偽碼類型:GOLD碼,內(nèi)存八組PN碼;

·BPSK調(diào)制: 載波中心頻率10.7MHz;

·動(dòng)態(tài)特性: 載波中心頻率變化范圍±100kHz,變化率≥±1.8kHz/s,偽碼變化范圍≥±300Hz。

DDS技術(shù)采用全數(shù)字結(jié)構(gòu),具有極高的頻率分辨率,極短的頻率轉(zhuǎn)換時(shí)間,輸出頻率相對(duì)帶寬很寬,具有程控靈活的優(yōu)點(diǎn),是傳統(tǒng)的模擬信號(hào)產(chǎn)生技術(shù)所無(wú)可比擬的。

前述的基于DDS和FPGA技術(shù)的高動(dòng)態(tài)擴(kuò)頻仿真信號(hào)源設(shè)計(jì)原理正確,輸出穩(wěn)定,實(shí)用中效果很好。在擴(kuò)頻通信高速發(fā)展的今天,高動(dòng)態(tài)擴(kuò)頻仿真信號(hào)源的應(yīng)用前景必將非常廣闊。

參考文獻(xiàn)

1 朱近康. 擴(kuò)展頻譜通信及其應(yīng)用,合肥:中國(guó)科學(xué)技術(shù)大學(xué)出版社,1995.10

2 樊昌信.通信原理. 長(zhǎng)沙:國(guó)防工業(yè)出版社,1995

3 林寶璽,胡志英.多譜勒雷達(dá). 長(zhǎng)沙:國(guó)防工業(yè)出版社,1982.11

4 AD9854 PRELIMINARY TECHNICAL DATA. 1999

評(píng)論