基于FPGA的棧空間管理器的研究和設(shè)計

在產(chǎn)生empty、full信號邏輯模塊設(shè)計時,采用了對輸入信號的每一位進(jìn)行組合邏輯判斷的方法,使該信號分兩路,一路作為與門組合邏輯的輸入信號產(chǎn)生full信號。如果輸入信號的每一位都為1, 則full信號置1,其他情況置0;另一路作為或門非組合邏輯的輸入信號產(chǎn)生empty信號。如果輸入信號的每一位都為0, 則empty置1,其他情況置0。在整個邏輯模塊設(shè)計中,采用組合邏輯設(shè)計,目的是縮短工作時延,提高系統(tǒng)工作頻率。

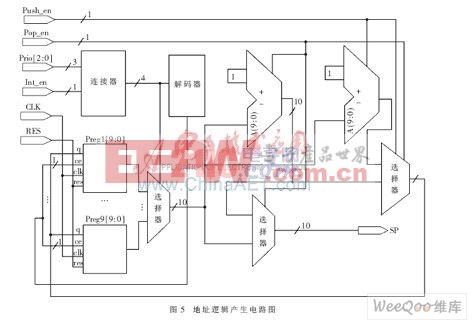

3.2 地址產(chǎn)生邏輯模塊設(shè)計

堆棧地址指針SP決定了堆棧空間單元的數(shù)據(jù)正確入棧和出棧,堆棧地址指針SP的獲得在于如何驅(qū)動讀/寫邏輯模塊和中斷棧模塊。為了確保被保護(hù)數(shù)據(jù)的有效性和實時性,防止出現(xiàn)不確定狀態(tài),須在時序同步的狀態(tài)下,對數(shù)據(jù)進(jìn)行操作,如圖5所示。

在地址產(chǎn)生邏輯設(shè)計時,先對堆棧地址寄存器組賦初值,該模擬系統(tǒng)管理8個任務(wù),有9個堆棧地址寄存器,分別為8個任務(wù)堆棧地址寄存器和1個中斷嵌套棧堆棧地址寄存器。

當(dāng)任務(wù)優(yōu)先級Prio信號和中斷使能int_en信號同時驅(qū)動多路選擇器時,堆棧地址指針SP從堆棧地址寄存器組中選擇存放在Pregx中的當(dāng)前任務(wù)的地址,在設(shè)計的棧空間管理器中,SP指向棧空間的下一個存儲單元的地址。如果入棧控制信號有效,則SP作為棧空間的尋址地址,寫入數(shù)據(jù),SP加1;如果出棧控制信號有效,則SP減1,改變后的SP值作為棧空間的尋址地址,讀出數(shù)據(jù)。操作完成后,改變后的SP值寫回到對應(yīng)的堆棧地址寄存器組Pregx中。

4 仿真結(jié)果分析

本棧空間管理器容量為10 KB,寬度為16 bit。在ISE 8.2i開發(fā)軟件中進(jìn)行了綜合和仿真,設(shè)計中使用了294個Slices芯片、396個觸發(fā)器芯片、274個input LUTs、60個bounded IOBs、1個塊BRAMs。

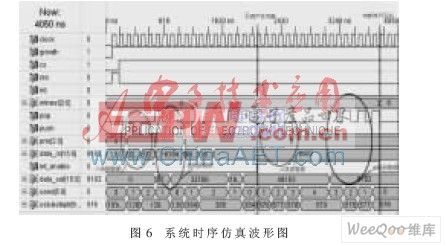

仿真時,輸入十進(jìn)制數(shù)的數(shù)據(jù),圖6為系統(tǒng)時序仿真波形圖。

(1)當(dāng)INT無效時,即系統(tǒng)中不存在中斷或中斷嵌套。在push有效的情況下,置prio信號值為2,data_in信號值分別為32 768、57 908。仿真時,輸出結(jié)果為:used信號值分別為1、2,而ostcbstkptr信號值分別為128、129;同理,在pop有效情況下,置prio信號值為2,觀察仿真結(jié)果為:dout_out信號值分別為32 768、57 908,used的信號值分別為1、0, ostcbstkptr信號值分別為129、128。由此可得,在無中斷處理的條件下,根據(jù)任務(wù)的優(yōu)先級prio,按LIFO原則在任務(wù)棧中寫入和讀出數(shù)據(jù),并且每次的有效操作同時修改當(dāng)前任務(wù)的used和ostcbstkptr信號值。

(2)當(dāng)INT 有效時,即系統(tǒng)中產(chǎn)生中斷或存在中斷嵌套。在push有效的情況下,置prio信號值為6及data_in信號值為8192,觀察仿真結(jié)果為:used信號值依次為1、2、3、4,ostcbstkptr信號值依次為576、577、578、579;同理,在pop有效情況下,置prio為6,此時的仿真結(jié)果:data_out信號值為8192,used信號值依次輸出4、3、2、1,ostcbstkptr信號值依次輸出579、578、577、576。由此可得,當(dāng)系統(tǒng)中產(chǎn)生中斷或存在中斷嵌套,按LIFO原則在中斷嵌套棧中寫入和讀出數(shù)據(jù),并且每次有效操作同時修改中斷嵌套棧的used和ostcbstkptr的值。

由以上結(jié)果分析可知,該實驗驗證了棧空間管理器的正確性,符合系統(tǒng)設(shè)計的要求。

本文分析了堆棧空間結(jié)構(gòu)及對被切換任務(wù)相應(yīng)數(shù)據(jù)信息的保護(hù),并對堆棧空間進(jìn)行了合理的結(jié)構(gòu)劃分。實驗數(shù)據(jù)表明了該系統(tǒng)的可行性和穩(wěn)定性。棧空間管理器能有效節(jié)約硬實時操作系統(tǒng)分配堆棧空間的時間,減少RAM存儲空間。從硬件角度上看,簡化了設(shè)計,降低了成本,具有一定的使用價值。目前只在實驗平臺上仿真,下一步擬將棧空間管理器的IP核應(yīng)用于硬實時操作系統(tǒng),以提高操作系統(tǒng)的運行效率。

評論