基于FPGA的棧空間管理器的研究和設(shè)計(jì)

中斷判斷邏輯由輸入信號(hào)INT與標(biāo)志寄存器位IntNeSTing值決定是否有效。如果有中斷發(fā)生,則中斷棧邏輯有效,中斷棧邏輯生成讀/寫地址,否則讀/寫地址邏輯有效,生成相應(yīng)的讀/寫地址。本文引用地址:http://www.104case.com/article/191537.htm

在讀/寫控制信號(hào)有效的情況下,從堆棧地址寄存器組中讀出當(dāng)前任務(wù)的地址,經(jīng)過讀/寫地址邏輯或中斷棧邏輯產(chǎn)生堆棧地址指針,作為HOS 堆棧空間的入棧/出棧地址。執(zhí)行入棧時(shí),在同步時(shí)鐘和入棧控制信號(hào)有效的情況下,中斷判斷邏輯判斷是否存在中斷或中斷嵌套,如果沒有,則由寫地址邏輯生成入棧地址;否則由中斷棧邏輯生成寫地址。同理,執(zhí)行出棧時(shí),在同步時(shí)鐘和出棧控制信號(hào)有效的情況下,中斷判斷邏輯判斷是否存在中斷或中斷嵌套,如果沒有,則讀地址邏輯生成出棧地址;否則中斷棧邏輯生成出棧地址。

為了快速、有效地保護(hù)被切換任務(wù)的信息,并滿足自動(dòng)檢驗(yàn)功能的要求,在棧空間管理器設(shè)計(jì)中設(shè)計(jì)了2個(gè)邏輯模塊,分別為狀態(tài)控制邏輯模塊和地址產(chǎn)生邏輯模塊。狀態(tài)控制邏輯模塊主要生成入棧/出棧控制信號(hào)和Used信號(hào),地址產(chǎn)生邏輯模塊主要生成有效的入棧/出棧地址。基于對棧空間管理器總體結(jié)構(gòu)工作過程的闡述,在Xilinx公司設(shè)計(jì)的XUP Virtex II Pro 系列的芯片上設(shè)計(jì)一個(gè)模擬棧空間管理器,模擬管理8個(gè)任務(wù),任務(wù)棧的深度為64,寬度為16 bit,中斷嵌套棧的深度為128,寬度為16 bit,容量為10 KB的堆棧空間。在設(shè)計(jì)管理器中,保證管理器快速綜合,使占用FPGA的資源盡可能少,存儲(chǔ)單元的選擇是關(guān)鍵,該系統(tǒng)采用的是FPGA上一個(gè)18 KB的Block RAM資源,使用ISE 8.2i提供的雙端口RAM存儲(chǔ)模塊的 IP核。如果選擇其他方法,如用觸發(fā)器和寄存器搭建存儲(chǔ)單元,則綜合時(shí)間長,且占用大量FPGA的 Slices資源。

在實(shí)際嵌入式系統(tǒng)應(yīng)用中,根據(jù)系統(tǒng)要求,可計(jì)算出棧空間深度和寬度,具體的深度和寬度在VHDL代碼中修改即可。

3.1 狀態(tài)控制邏輯模塊設(shè)計(jì)

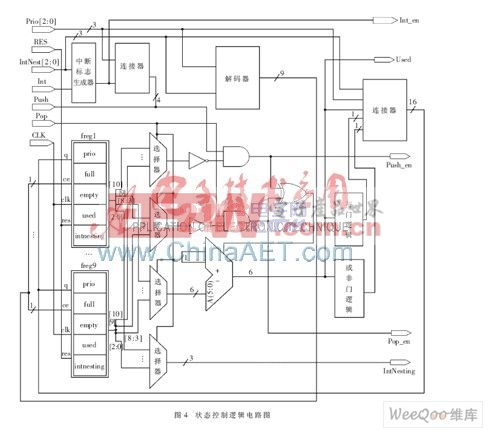

由于狀態(tài)標(biāo)志寄存器的空/滿狀態(tài)標(biāo)志位決定棧空間入棧/出棧操作,所以如何設(shè)計(jì)空/滿狀態(tài)標(biāo)志位是關(guān)鍵。為了保護(hù)的數(shù)據(jù)能正確入棧與出棧,防止存儲(chǔ)器出現(xiàn)向上溢出或向下溢出,保證在滿的情況下,不能進(jìn)行push操作;在空的狀態(tài)下,不能進(jìn)行pop操作。控制信號(hào)的產(chǎn)生過程如圖4所示。

在狀態(tài)控制邏輯模塊設(shè)計(jì)時(shí), prio_int信號(hào)驅(qū)動(dòng)4個(gè)多路選擇器,選擇對應(yīng)狀態(tài)標(biāo)志寄存器組中的各位段,分別有full信號(hào)值、empty信號(hào)值、fcount信號(hào)值和intNesting信號(hào)值。 empty/full信號(hào)和push/pop信號(hào)作為組合邏輯輸入信號(hào)產(chǎn)生相應(yīng)的push_en/pop_en有效控制信號(hào),該控制信號(hào)決定棧空間是否執(zhí)行入棧/出棧操作。

在push_en/pop_en控制信號(hào)有效的情況下,驅(qū)動(dòng)二進(jìn)制運(yùn)算邏輯加/減1,輸出運(yùn)算結(jié)果。輸出的信號(hào)值有3個(gè)用途:(1)作為空/滿標(biāo)志狀態(tài)產(chǎn)生邏輯的輸入信號(hào),該信號(hào)邏輯產(chǎn)生empty/full信號(hào);(2)寫回到fregx對應(yīng)的fcount位中;(3)作為Used輸出信號(hào)值,表示當(dāng)前任務(wù)棧或中斷嵌套棧的使用情況。

評論