一種基于FPGA的正弦波信號發生器的設計

1.5 低通濾波電路

低通濾波器用于濾除階梯信號中的諧波分量。本文采用2階低通濾波電路,階梯信號通過低通濾波,使得輸出信號頻譜純度較好,失真較小。本文引用地址:http://www.104case.com/article/191487.htm

2 系統關鍵技術

DDS(Direct Digital Synthesis)是一種應用直接數字合成技術來產生信號波形的方法。DDS技術建立在采樣定理的基礎上,它首先對需要的信號波形進行采樣、量化,然后存入存儲器作為待產生信號的數據查詢表。在輸出信號波形時,從數據表依次讀出數據,產生數字信號。

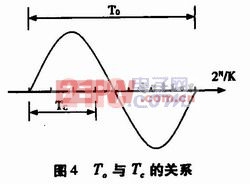

輸入時鐘頻率和輸出波形信號的頻率關系如圖4所示。在圖4中To表示輸出波形的周期,Tc為采樣周期,2N為ROM查詢表尋址范圍,K為頻率控制字。由圖可知To=Tc*2N/K,轉換為頻率可表示為fo=fc*K/2N,fc為時鐘信號clk的頻率。

在本設計中N=8,因此信號的輸出頻率fo=fc*K/256。

3 軟件設計

軟件設計主要是在FPGA中通過Verilog硬件語言進行相位累加器和ROM查詢表的編程實現,這兩部分采用Quartus軟件和Matlab軟件并行開發。

3.1 相位累加器的實現

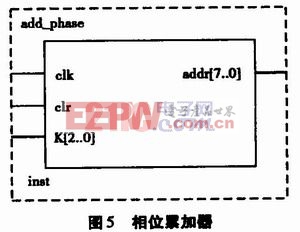

相位累加器主要用于產生ROM查詢表所需的地址信息。圖5為在Quartus軟件中編程生成的相位累加器符號,相位累加器的輸入信號包括時鐘信號clk、復位信號clr和頻率控制字K。輸出信號addr[7…0]為ROM查詢表的輸入地址信號。

相位累加器類似一個計數器。首先,軟件設置相位累加器的基數為0,并通過時鐘信號clk上升沿觸發,基數與頻率控制字K相加,相加后的值反饋到相位累加器的輸入端作為下一次的基數。當相位累加器的溢出時,—個完整的階梯正弦信號就從ROM查詢表的輸出端輸出。因此,相位累加器的溢出率就是正弦波信號的輸出頻率。相位累加器的仿真波形如圖6所示。

評論