基于FPGA的數(shù)字幅頻均衡功率放大器的解決方案

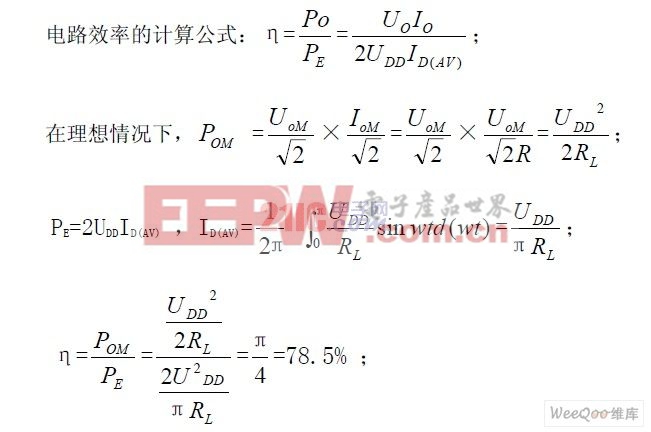

實際功率低于這個值,通過測量來計算出電路的效率。

3 軟件設(shè)計

Altera 提供了基于Matlab、DSP Builder 的數(shù)字濾波器設(shè)計方法。使用DSP Builder可以方便地在圖形化環(huán)境中設(shè)計FIR 濾波器,而且濾波器系數(shù)可以通過Matlab 的濾波器設(shè)計工具FDATool 計算完成。本文中采用直接I 型來實現(xiàn)該FIR 濾波器。首先設(shè)計一個系數(shù)可變的4 階FIR 濾波器節(jié)。然后再通過不斷的調(diào)用FIR 濾波器節(jié),級聯(lián)起來,從而完成高階濾波器設(shè)計。

4 實驗結(jié)果與結(jié)論

圖4 singaltap 測試結(jié)果

圖 4 為采用嵌入式邏輯分析儀SingalTap 得到的測試結(jié)果。其中,XIN 為由A/D 采樣得到的輸入信號,YOUT 為經(jīng)過均衡程序處理過的輸出信號。從輸出YOUT 可明顯觀測到程序?qū)斎胄盘栕鞒隽搜a償,去除了噪聲,穩(wěn)定了波形,起到了均衡信號的作用。本設(shè)計充分利用 FPGA 在數(shù)字信號處理上的優(yōu)勢,在數(shù)字幅度均衡模塊中以FPGA 為平臺,實現(xiàn)數(shù)字信號幅度均衡的高速處理。同時本設(shè)計中前級放大電路不僅可以滿足賽題中的各項指標(biāo),還可以實現(xiàn)增益的可選擇性,可以在其他小信號放大的場合中運用。

評論