MAX1032結合CPLD的應用

本文引用地址:http://www.104case.com/article/191480.htm

本文引用地址:http://www.104case.com/article/191480.htm

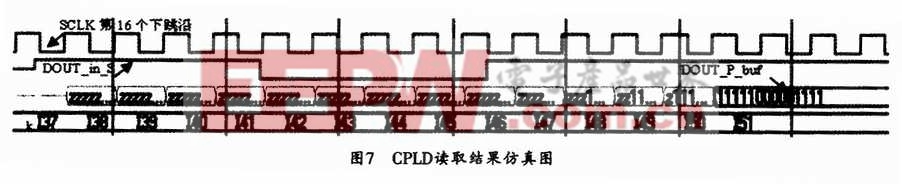

圖7所示是Moddsim仿真的CPLD讀取MAX1032的采樣結果并將其存入寄存器DOUT_P_buf的仿真圖。由圖可見,在啟動采樣后的第16個SCLK的下跳沿,MAX1032輸出14位串行采樣結果,CPLD將其存入內部寄存器中以待系統讀取。一般在下一次采樣之前,需要將CPLD復位來清除上一次采樣的數據。由于外部時鐘模式下的SSTRB始終為低,故本例沒有對該信號進行處理。

5 結束語

本文介紹了利用CPLD控制MAX1032進行采樣的實現方法,包括CPLD的內部邏輯設計和對采樣信號的處理等。實驗證明,該方法能夠適用

需要使用CPLD控制外圍電路的場合。

評論