利用 IDDR 簡化亞穩態

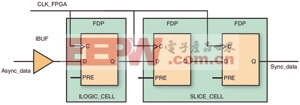

圖1 同步器鏈的默認布置圖

圖中,將寄存器鏈放置在兩個單元中:第一個為ILOGIC單元,而另外兩個寄存器放置在SLICE單元中(選擇具有相同時鐘的3個寄存器和鏈)。這是減少亞穩態問題的一種快速且非常簡單的方法,還有其他一些方法不但可減少亞穩態問題,還可優化性能。

使用賽靈思邏輯塊的IDDR方法

在Virtex-4和Virtex-5 FPGA中,賽靈思將其ILOGIC模塊直接放置在I/O驅動器和接收器的后面。該模塊包括4個存儲元件寄存器和1個可編程絕對延遲元件。

Virtex-4與Virtex-5器件均采用這4個寄存器來實現雙倍數據率輸入(IDDR)寄存器,功能設計師只需例化IDDR原語便能實現。這將使 受益匪淺。

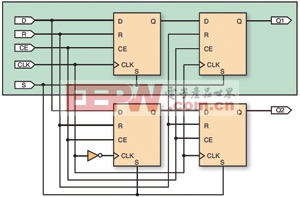

這種原語的其中一個模式稱為SAME_EDGE_PIPELINED。圖2顯示了采用這種模式的DDR輸入寄存器及相關信號。綠色矩形框顯示了一系列最優的寄存器,可用其解決亞穩態問題。此外,使用 IDDR 方法還有一個優勢,即能使用兩三倍之多的主時鐘,同時又不會造成任何設計時延問題。

圖2 SAME_EDGE_PIPELINED模式中的輸入DDR

只需少量代碼

在《Virtex-4用戶指南》的328~329頁,舉例說明采用VHDL和Verilog語言編寫的IDDR原語的例化。以下采用Verilog語言的IDDR原碼例化的典型實例:

defparam IDDR_INT2.DDR_CLK_EDGE = SAME_EDGE_PIPELINED;

defparam IDDR_INT2.INIT_Q1 = 1'b1;

defparam IDDR_INT2.INIT_Q2 = 1'b1;

defparam IDDR_INT2.SRTYPE = SYNC;

IDDR IDDR_INT2( .Q1(sync_data),

.Q2(signal_noload), .C(CLK_2X),

.CE(1'b1), .D(async_data),.R(), .S());

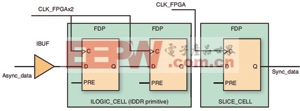

在圖3中看到全新的布局圖。 用這種方法將寄存器鏈放置在兩個單元:前兩個寄存器放置在ILOGIC單元中,另一個寄存器則放置在SLICE單元中(這里選擇的鏈具有3個寄存器和2個不同的時鐘,其中一個時鐘速度是另一個的兩倍)。

圖3 顯示IDDR替代的同步器鏈

整體而言,亞穩態問題會給設計帶來不便,但采用一些快速便捷的解決方案(如以一種新的方式使用IDDR原語)就能大幅降低設計發生亞穩態問題的幾率。大家應在創建設計時就采用上述方法,而不應事后亡羊補牢,這樣就能創建出既能靈活應對亞穩性問題,而且所占面積、性能和成本又得到優化的架構。

評論