脈沖壓縮原理及FPGA實現

3 64階匹配濾波器設計及仿真

由于匹配濾波器就是有限脈沖響應濾波器,具有線性特性,所以通過低階濾波器的直接級聯相加就可以實現高階濾波器,前一個濾波器的移位數據y_out作為下一個濾波器模塊信號的輸入,每個濾波器模塊都與4階FIR設計相同,只需根據不同系數更改查找表中的數據。

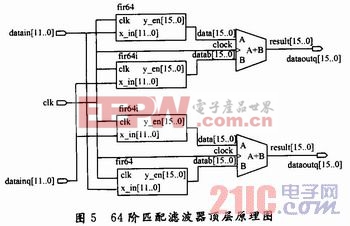

在64階匹配濾波器設計中,先用16個4階的FIR濾波器級聯成一個64階的FIR濾波器,然后再用4個64階的FIR濾波器組成一個64階的匹配濾波器,即64階的脈沖壓縮濾波器。64階脈沖壓縮濾波器的邏輯設計如圖5所示。

邏輯設計是以Altera公司的cycloneⅡ系列EP2C70為平臺,在QuartusⅡ軟件中利用VHDL語言和原理圖進行邏輯設計,頂層為原理圖,底層為VHDL文件。圖5中,fir64模塊為匹配濾波器實部對應的64階濾波器,fir64I模塊為匹配濾波器虛部對應的64階濾波器,輸出為16 位的I、Q兩路信號。由Matlab軟件仿真出來的匹配濾波器的系數全部是小數,然后進行歸一化處理后得到匹配濾波系數。脈沖壓縮加權不涉及硬件規模的增加,只是對其系數乘以一個適當的加權函數,在實際的編程實現過程中與不加權的處理方法是完全一致的。

對該匹配濾波器進行波形仿真,輸入為12位的有符號數據,系數為12位有符號數據,輸出為16位有符號數據。由于匹配濾波器做的是64×64點的卷積,所以輸出數據為64+64-1=127個。由于仿真數據較多,只給出了部分仿真結果,如圖6所示。

4 結語

仿真分析表明,脈壓輸出的實際值與Matlab仿真值十分接近,其誤差是由量化所產生的,系統具有很高的精度。通過仿真分析整個設計,可得出利用基于分布式算法能夠大大減少數字脈沖壓縮的運算量,減少FPGA的資源消耗。另外還可以根據不同的需求,增加脈沖壓縮階數,更高階數的脈沖壓縮實現方法與64階的完全一致。由于匹配濾波器的系數對稱,所以可采用線性相位FIR濾波器在FPGA中的實現算法,這樣同等性能的濾波器設計可減小一半的硬件規模,這樣就會節省更多的邏輯單元,實現更多的功能。

本文引用地址:http://www.104case.com/article/191422.htm

評論