脈沖壓縮原理及FPGA實現

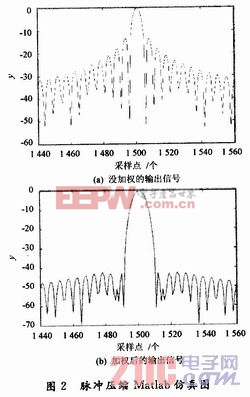

下面,給出仿真信號模型,并在Matlab下進行仿真,以分析加權前后的影響。仿真模型:脈沖寬度為150μs,調頻帶寬為2 MHz,采樣周期為0.1μs,加權方式為海明加權。圖2給出了采用加權函數前和采用海明加權函數后的脈沖壓縮波形圖。

通過海明加權,主副瓣比大大改善,即副瓣得到了顯著的抑制。雖然海明加權后帶來了一定的信噪比損失,但匹配濾波器的性能得到了大大的提高。

2 分布式算法原理及4階FIR濾波器的設計

2.1 分布式算法原理

分布式算法(DA)是一種以實現乘累加運算為目的的運算方法,它與傳統乘加運算的不同在于執行部分積運算的先后順序不同。傳統算法是在完成乘加功能時,等到所有乘積產生之后,再進行相加來完成乘加運算的。而分布式算法則是通過將各輸入數據的每一對應位產生的部分積預先進行相加,形成相應部分積,然后對各部分積進行累加,形成最終結果的。與乘累加算法相比,分布式算法可極大地減少硬件電路規模,降低設計的復雜度,極大地提高可靠性和可操作性。分布式算法由串行、并行和串并結合而構成的分布式算法。串行分布式算法是逐位的執行,每個時鐘周期只能執行1位,速度比較慢;并行分布式算法是1個時鐘周期完成1個字的運算,速度比較快;串并結合的分布式算法

1次可以執行多位,但是需要多個時鐘周期才能完成1個字的運算,控制起來比較復雜。

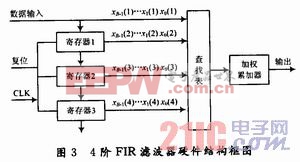

根據分布式算法的原理得出采用FPGA實現分布式算法的硬件結構,如圖3所示。

圖3中寄存器完成數據寄存,查找表完成數據查找運算,加權累加器完成查表之后的加法。為了保證信號的完整性,即減少輸出毛刺,在數據輸出前用寄存器寄存一個時鐘周期然后輸出。

2.2 4階FIR濾波器的設計

本文的脈沖壓縮是通過并行分布式算法來實現的。從圖3可以得出,4階的FIR濾波器主要由移位寄存器、查找表和累加器組成。4為模塊的濾波器階數,那么查找表中應有24個存儲單元,如果濾波器階數過多,查找表規模隨階數的增加成指數遞增,因此階數較大時要分割查找表,分割查找表可以節省存儲資源,有利于成本和資源的節約。

要使4階FIR濾波器完成數據的輸入、串/并轉換、查表和加權累加,因為是有符號數的運算,所以要考慮累加最高位運算符號。FIR濾波器是線性濾波器,低階濾波器的輸出集合相加,形成一個高階FIR濾波器的輸出。因此,在設計低階FIR時,必須有2個輸出,一個用于FIR運算的輸出,另一個輸出數據用于下一個FIR濾波器的運算。為了保證信號的完整性,在程序設計時,對輸入/輸出數據進行了寄存處理。

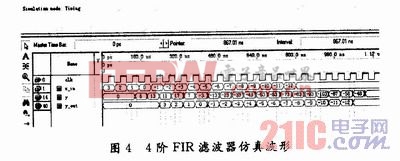

下面給出一個4階的FIR濾波器設計實例。輸入數據為12位有符號數,匹配濾波系數為12位有符號數,4階FIR的仿真波形如圖4所示。仿真結果與Matlab仿真結果完全一致,說明設計是完全正確的。

評論