一種全新的深亞微米IC設(shè)計方法

本文分析了傳統(tǒng)IC設(shè)計流程存在的一些缺陷,并且提出了一種基于Logical Effort理論的全新IC設(shè)計方法。

本文引用地址:http://www.104case.com/article/191413.htm眾所周知,傳統(tǒng)的IC設(shè)計流程通常以文本形式的說明開始,說明定義了芯片的功能和目標性能。大部分芯片被劃分成便于操作的模塊以使它們可以分配給多個設(shè)計者,并且被EDA工具以塊的形式進行分析。邏輯設(shè)計者用Verilog或VHDL語言寫每一塊的RTL描述,并且仿真它們,直到這個RTL描述是正確的。

得到RTL描述之后,接下來就是利用邏輯綜合工具來選擇電路的拓撲結(jié)構(gòu)和門的大小。綜合工具比手工花更少的時間得到優(yōu)化路徑和電路圖。綜合的電路通常邏輯功能是正確的,但時序是基于近似負載模型評估得到的。

電路設(shè)計完成之后,開始版圖的實現(xiàn)。版圖通常可以定制也可以用自動布局布線工具產(chǎn)生。接下來,DRC、ERC、LVS等被用來驗證版圖,后版圖時序驗證工具用從版圖提取出來的電阻、電容數(shù)據(jù)來驗證設(shè)計是否滿足時序目標。如果電路設(shè)計階段的時序評估不精確,版圖后的時序肯定不能滿足,電路必須被修改,再執(zhí)行綜合到版圖的過程。

在電路設(shè)計過程中,最大的挑戰(zhàn)是滿足時序說明,即時序收斂。如果時序沒有問題,電路設(shè)計將變得更加容易。目前的EDA界都意識到這一點:要想在版圖階段達到時序收斂,通常應該在綜合階段就考慮更多的物理設(shè)計信息。因此,現(xiàn)在很多工具在綜合階段進行預布局布線,以便在綜合階段盡可能多地了解后端信息。

其實這樣做并不是從本質(zhì)上解決問題,因為在綜合階段的時序評估還是基于負載模型的理論,只是現(xiàn)在的模型比以前的要精確一些,但是與實際的版圖提取的負載還是有誤差,因此得到的時序收斂并不一定可信。不過這些方法可以減少迭代次數(shù),但不能真正消除迭代。

為了預知時序,其實應該建立一個非常可信的延遲預算模型,也就是這個模型的延遲預算應該非常可信。可信是指如果它預知電路1比電路2要快,那么實際中確實是這樣。但是基于負載模型的方法不是非常可信,它需要精確的寄生參數(shù)信息,但在版圖沒有得到的情況下,你是不可能有精確的寄生參數(shù)信息的。因此需要建立另外一個延遲模型,使得它不需要寄生參數(shù)信息也能得到可信的延遲估算。

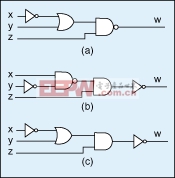

Logical Effort方法采用的延遲預算模型就是這樣的一個模型,Logical Effort方法是評估CMOS電路延遲的一個簡單方法。該方法通過比較不同邏輯結(jié)構(gòu)的延遲來選擇最快的候選者,該方法也能指定一條路徑上適當?shù)倪壿嫚顟B(tài)數(shù)和邏輯門的最好晶體管大小。它是設(shè)計早期評估可選方案的理想方法,并且為更加復雜的優(yōu)化提供了一個好的開始。

Logical Effort延遲模型

建模延遲的第一步是隔離特定的集成電路加工工藝對延遲的影響。通常,把絕對延遲表示為兩項之積:一項是無單位的延遲d,另一項是特征化給定工藝的延遲單位τ。即dabs=dτ。τ可以計算出來,例如在0.6μm工藝下τ大約為50ps。

延遲d通常由兩部分組成,一部分叫本征延遲或寄生延遲,表示為p,另一部分正比于門輸出端負載的延遲,叫做effort延遲,表示為。即:d=f+p。

effort延遲依賴負載和邏輯門驅(qū)動負載的特性。我們引入兩個相關(guān)的項:Logical Effort(LE)捕捉邏輯門的特性,electrical effort(g)特征化負載的影響。即f=LE*g,所以d=LE*g+p。

Logical Effort捕捉邏輯門的拓撲結(jié)構(gòu)對它產(chǎn)生輸出電流的影響,它獨立于晶體管的大小。electrical effort即門的增益,描述門的電子環(huán)境(即與門連接的東西)怎樣影響它的性能,也可以說門中晶體管的大小怎樣決定門的負載驅(qū)動能力。增益的簡單定義是:g=Cout/Cin。其中Cout為邏輯門輸出端負載的電容,Cin為邏輯門輸入端的電容。

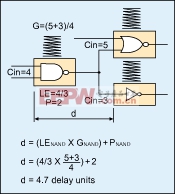

至此,我們可以如圖1所示那樣來計算延遲d。

從這里我們看到,延遲依賴門的增益,而不是它的精確寄生參數(shù)。同時,Logical Effort理論中還有兩個非常完美的結(jié)論。

少的邏輯狀態(tài)不一定能產(chǎn)生最快的電路延遲。那么多少個邏輯狀態(tài)將產(chǎn)生最快的電路延遲呢?對于反向器組成的電路,Sutherland指出:最快的反向器結(jié)構(gòu)發(fā)生在Cout=3.6Cin。當Cout=3.6Cin時,我們稱反向器的負載為完美負載。我們可以定義門的增益為Gain=Cout/(3.6*Cin),并把它作為電路單元(cell)的延遲預算。

最快的電路拓撲結(jié)構(gòu)有一致可變的Gain,因此在物理綜合階段,可以通過仔細調(diào)整Gain的值,保持時序不變。

評論