通過左移DRC設計規則檢查方法降低IC設計復雜性

最成功的半導體公司都知道,集成電路 (IC) 設計日益復雜,這讓我們的傳統設計規則檢查 (DRC) 方法不堪重負。迭代的“通過校正構建”方法適用于更簡單的自定義布局,但現在卻造成了大量的運行時和資源瓶頸,阻礙了設計團隊有效驗證其高級設計和滿足緊迫的上市時間目標的能力。為了克服這種設計復雜性,主要半導體公司不斷從其生態系統合作伙伴那里尋找有效的工具。西門子 EDA 是一家大型電子設計自動化 (EDA) 公司,它提供了一種新的、強大的左移驗證策略,他們對其進行了評估并宣布它改變了他們早期設計階段的游戲規則。

本文引用地址:http://www.104case.com/article/202503/467745.htm左移如何應對現代 IC 設計的挑戰

電子行業不斷發展,不斷創新和改變集成電路的基本方面。整個生態系統都會做出反應并推動改進,從而產生更快、更小、更強大的 IC。對于制造前的物理設計和布局驗證,我們曾經可以依靠手動的定制流程。這已經讓位于高度自動化的工作流程和多層設計層次結構。由于不同的設計組件是由不同的設計團隊在不同的時間表上開發的,因此要有一個完全組裝的設計布局可用于全面驗證變得極其困難。此外,當今高級工藝設計規則的龐大數量和復雜性加劇了制造前所需的關鍵設計規則檢查 (DRC) 的運行時間和計算要求。

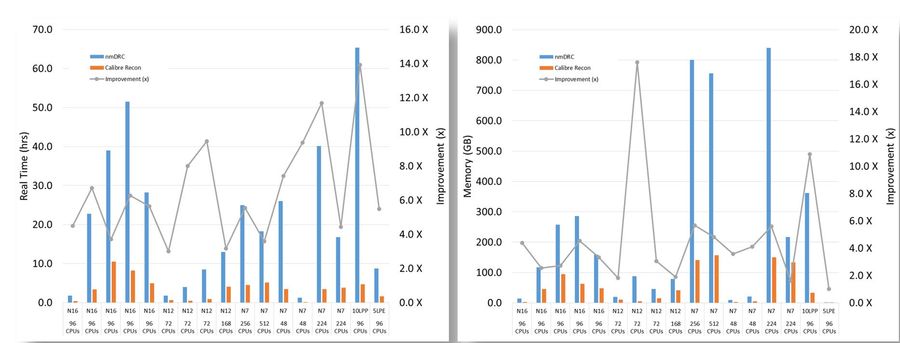

解決方案在于在設計過程的早期移動驗證步驟——這種策略稱為“左移”驗證。通過將驗證移至更接近設計更改源的位置,左移方法可以顯著縮短調試時間,管理不完整的數據并加快流片路徑。傳統 DRC 運行和左移 DRC 運行之間的運行時間和內存差異很大,如圖 1 所示。

圖 1.與 Calibre nmDRC(藍色條)相比,Calibre nmDRC Recon(橙色條)的運行時間和內存改進。西門子 EDA

圖 1.與 Calibre nmDRC(藍色條)相比,Calibre nmDRC Recon(橙色條)的運行時間和內存改進。西門子 EDA

主要半導體公司正在使用 Siemens EDA 的左移 DRC 工具(稱為 Calibre DRC Recon)取得成功。該工具有效性的關鍵在于它能夠僅識別和運行范圍內的本地規則,而不是在整個設計中執行全面的 DRC 檢查。與傳統的 DRC 方法相比,這種“本地檢查”方法大大降低了運行時和硬件要求。

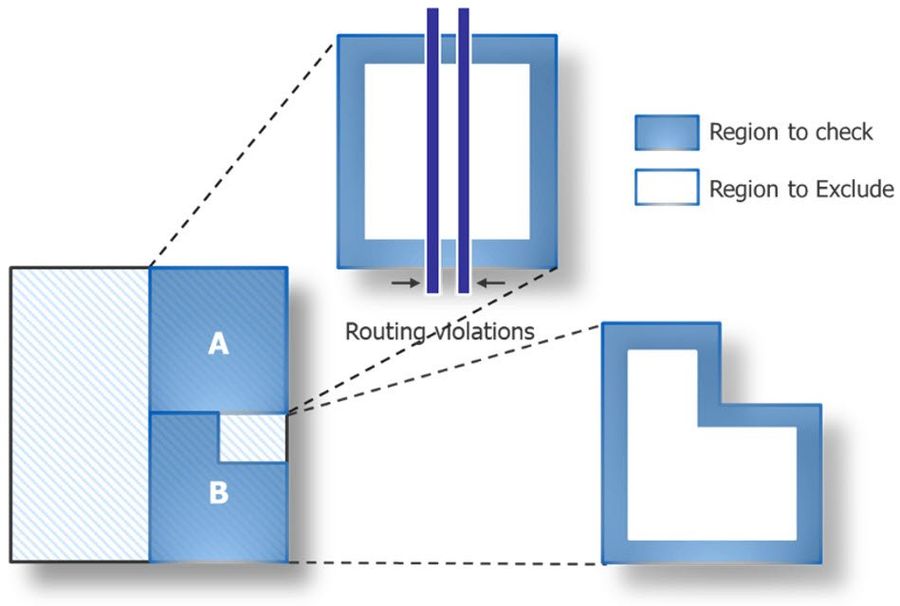

作為對本地檢查方法的補充,設計人員還可以使用自動豁免功能來識別和排除設計中已知不完整的區域,從而消除它們進行檢查,從而避免錯誤違規減慢驗證過程。這是一種通過自動豁免實現的灰箱技術,如圖 2 所示。

客戶的左移 DRC 成功案例

一家領先的技術公司親眼目睹了使用 Calibre DRC Recon 采用左移驗證策略的好處。設計團隊能夠顯著降低運行時和硬件要求,同時提高整體生產力。設計人員在平面圖階段開始使用 Calibre nmDRC Recon 迭代,然后在物理實現階段。到那時,大多數設計都沒有電源和接地網絡的短路。他們能夠及早發現任何問題,同時仍然很容易直接在布局環境中修復。由于這些修復是使用簽核準確的 Calibre 規則進行的,因此團隊知道結果是可靠且高度準確的。圖 3 說明了不同 DRC 方法的運行時改進。

圖 3.使用左移 DRC 時,運行時間顯著縮短。西門子 EDA

圖 3.使用左移 DRC 時,運行時間顯著縮短。西門子 EDA

設計人員的經驗展示了左移驗證在實際應用中的強大功能。通過利用本地檢查方法和互補功能(如自動豁免和分牌運行),該團隊能夠加快其設計迭代并縮短上市時間。

運行時的改進是顯著的,與傳統的 DRC 方法相比,左移 DRC 工具的性能提高了 15 倍。此外,內存使用量減少了 18 倍,使設計團隊能夠最大限度地提高其計算資源的利用率。

采用左移思維方式,加快 IC 設計速度

隨著 IC 設計的復雜性不斷升級,設計團隊不能再依賴傳統的 DRC 方法來跟上步伐。左移驗證策略提供了一個引人注目的解決方案,可解決現代設計組織面臨的關鍵挑戰。

通過專注于本地檢查、利用自動豁免和優化并行執行,左移 DRC 加快了設計和驗證過程,簡化了調試,并最終更快地將創新產品推向市場。該案例研究有力地證明了這種方法的變革性影響,突出了設計團隊可以實現的顯著生產力提升和效率提升。

對于希望保持領先地位的設計團隊來說,采用左移思維方式進行物理驗證至關重要。Siemens EDA 的先進 DRC 工具提供了一條行之有效的前進道路,使設計人員具備駕馭現代 IC 設計復雜性所需的能力,并以前所未有的速度和效率將其尖端產品推向市場。

評論