視頻圖像灰度信號(hào)直方圖均衡的FPGA實(shí)現(xiàn)

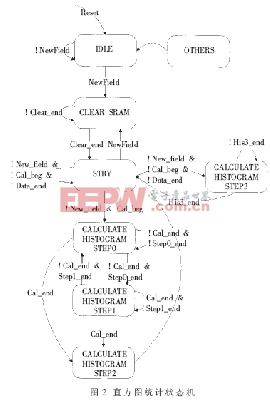

每當(dāng)一個(gè)新的圖像數(shù)據(jù)進(jìn)入統(tǒng)計(jì)模塊,就將SRAM內(nèi)相應(yīng)地址的統(tǒng)計(jì)數(shù)據(jù)讀出,累加后再存入該地址。由于前后數(shù)據(jù)可能是一樣的,會(huì)造成對(duì)同一個(gè)SRAM地址同時(shí)讀寫而引起錯(cuò)誤。這就需要一個(gè)模塊對(duì)整個(gè)過程加以控制。基本的思路是:對(duì)前后數(shù)據(jù)進(jìn)行比較,若前后數(shù)據(jù)相等就將計(jì)數(shù)器累加,直到發(fā)現(xiàn)數(shù)據(jù)不等才將統(tǒng)計(jì)數(shù)據(jù)寫入SRAM,這樣就從根本上避免了讀寫同一個(gè)地址的可能性。直方圖統(tǒng)計(jì)狀態(tài)機(jī)實(shí)現(xiàn)框圖如圖2所示。

由于使用了乒乓模式(一塊SRAM用于當(dāng)前場的統(tǒng)計(jì),另一塊用于前一場灰度均衡的計(jì)算),狀態(tài)機(jī)在上電復(fù)位后首先需要將用于統(tǒng)計(jì)的SRAM清空,這可以利用視頻的場消隱時(shí)間加以處理(相應(yīng)的狀態(tài)機(jī)狀態(tài)是CLEAR SRAM狀態(tài)),然后等待有效數(shù)據(jù)進(jìn)入(對(duì)應(yīng)于STBY狀態(tài)),一旦有效灰度數(shù)據(jù)進(jìn)入,狀態(tài)機(jī)就進(jìn)入統(tǒng)計(jì)狀態(tài)0(CALCULATION HISTOGRAM STEP0)。此時(shí),首先讀出SRAM相應(yīng)于該灰度值的數(shù)據(jù),同時(shí)將數(shù)據(jù)延遲并觀察前后數(shù)據(jù)是否相同,如相同則繼續(xù)停留在該狀態(tài),將計(jì)數(shù)器加1;否則進(jìn)入統(tǒng)計(jì)狀態(tài)1(CALCULATION HISTOGRAM STEP1)。進(jìn)入狀態(tài)1后,計(jì)算上一個(gè)灰度值的統(tǒng)計(jì)數(shù)據(jù)(將從SRAM中讀出的值加上計(jì)數(shù)器的值再加1)存入SRAM,同時(shí)還要讀出SRAM里相應(yīng)于當(dāng)前灰度值的數(shù)據(jù)。此后的工作與狀態(tài)0相似。以此類推,狀態(tài)不斷在狀態(tài)0和狀態(tài)1之間切換,直到有效數(shù)據(jù)結(jié)束后進(jìn)入統(tǒng)計(jì)狀態(tài)2(CALCULATION HISTOGRAM STEP2),狀態(tài)2 的作用是將這一行的最后一個(gè)灰度數(shù)據(jù)的統(tǒng)計(jì)信息寫入SRAM。隨后回到STBY狀態(tài),等待下一行數(shù)據(jù)。當(dāng)所有有效行都統(tǒng)計(jì)完后,進(jìn)入狀態(tài)機(jī)的統(tǒng)計(jì)狀態(tài)3(CALCULATION HISTOGRAM STEP3),重新將灰度統(tǒng)計(jì)數(shù)據(jù)累計(jì)后存入SRAM。

4 SDRAM 控制器的實(shí)現(xiàn)結(jié)構(gòu)

輸入輸出視頻圖像的速度(13.5MHz)遠(yuǎn)低于SDRAM的最高速度(143MHz),假如以單個(gè)數(shù)據(jù)對(duì)SDRAM讀寫(Single Write/Single Read),根本無法發(fā)揮SDRAM高速的優(yōu)勢(shì),所以必須使用SDRAM的突發(fā)模式(BURST MODE),即一次讀出或者寫入多個(gè)數(shù)據(jù)。以美光公司(MICRON)MT48LC1M16A1S SDRAM為例,它支持1、2、4、8個(gè)字或者整頁(256個(gè)字)的讀寫。由于屬于兩個(gè)時(shí)鐘域,所以必須對(duì)寫入或者讀出SDRAM的數(shù)據(jù)緩存。在這里,讀寫模塊分別使用兩個(gè)深度為64、寬度為16bit的雙口SRAM以乒乓的方式加以實(shí)現(xiàn)。一次突發(fā)模式讀寫的數(shù)據(jù)量都是64個(gè)字,因此選擇深度為64的SRAM是一種折衷的辦法,數(shù)據(jù)過少無法發(fā)揮突發(fā)模式的優(yōu)勢(shì),數(shù)據(jù)過大則需要更多的SRAM作為緩存,使開銷過高。實(shí)踐證明一次讀寫64個(gè)數(shù)據(jù)比較合適。

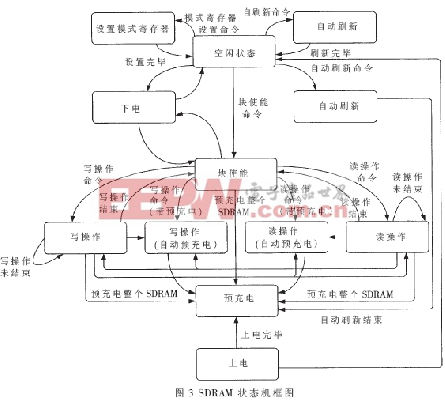

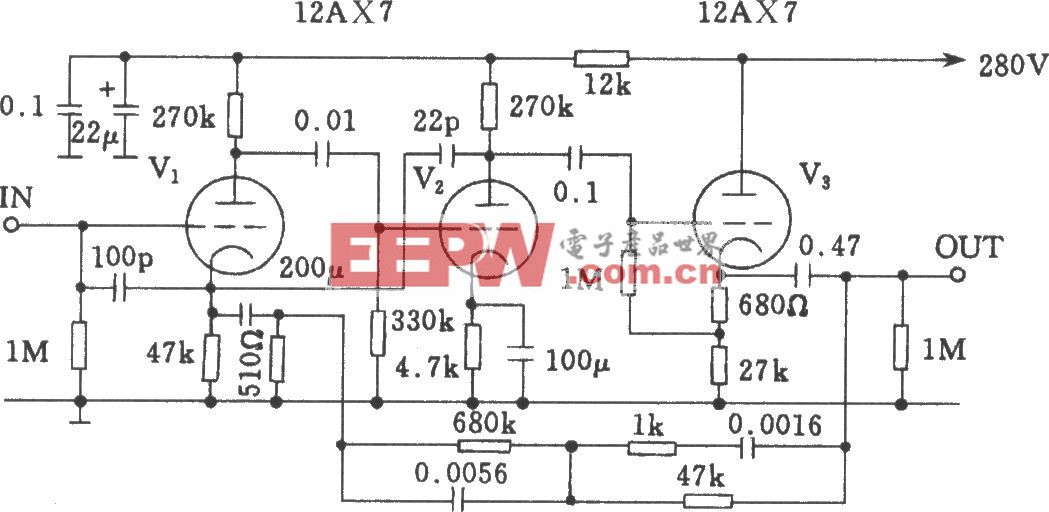

由于SDRAM結(jié)構(gòu)的特殊性,它的讀寫刷新操作需要滿足一定的時(shí)序要求,所以需要專門的控制器來維護(hù)對(duì)SDRAM的操作。圖3是Hynix Electronics公司HY5DV641622AT 的SDRAM的狀態(tài)機(jī)框圖,該框圖包含SDRAM上電時(shí)序、模式寄存器的設(shè)置、讀寫控制、預(yù)充電和定時(shí)刷新等多個(gè)環(huán)節(jié)。控制器的具體實(shí)現(xiàn)可以參考Xillinx或者Altera公司相關(guān)文檔和各家DRAM廠商的資料。

評(píng)論