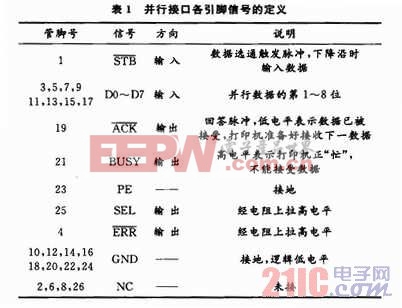

微型打印機與FPGA的硬件接口及軟件設(shè)計

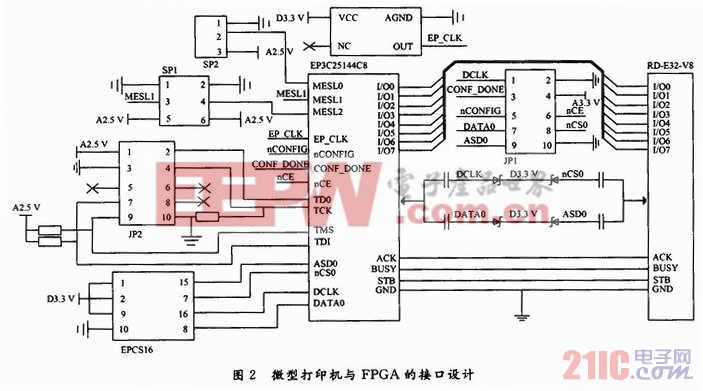

設(shè)計控制功能模塊時,由于FPGA有富余的I/O接口,所以打印機可以不經(jīng)過另外的接口電路而直接與FPGA相連接,同時FPGA其內(nèi)部的嵌入式陣列塊 EAB是輸入端口和輸出端口都帶有觸發(fā)器的RAM塊,可實現(xiàn)小容量的ROM和RAM,無需外部擴展ROM和RAM,也無需外加鎖存器。FPGA芯片可以通過編程配置其內(nèi)部邏輯單元,通過編寫軟件來設(shè)計微型打印機控制器,所以只需分配好與打印機相連接的I/O接口,讀寫相連的信號線即可。打印機的BUSY,和D0~D7信號接口分別由FPGA在編程綜合過程中分配通用I/O接口,接口方式如圖2所示。

本文引用地址:http://www.104case.com/article/191405.htm

本文引用地址:http://www.104case.com/article/191405.htm

圖中JP1和JP2是FPGA的配置接口,JP1與EPCS16SI16N外部存儲芯片一起,構(gòu)成FPGA的串行(AS)配置端口,當程序調(diào)試完成后,可將程序經(jīng)JP2口下載至配置芯片EPCS16SI16N,F(xiàn)PGA上電之后,系統(tǒng)自動將配置芯片中的程序讀入FPGA內(nèi),完成邏輯功能塊的配置。JP1是 JTAG配置口,主要作用是方便程序的現(xiàn)場調(diào)試,不需經(jīng)過外部存儲器,程序直接下載到FPGA中完成邏輯功能塊的配置,以驗證程序設(shè)計能否實現(xiàn)預(yù)期的功能。SP1與SP2用以設(shè)置配置芯片與FPGA數(shù)據(jù)傳輸?shù)墓ぷ鞣绞剑鏜ESL2,MESL1,MESL0為“010”時,配置為標準串行端口,配置電壓為3.3 V;若為“100”時為快速串行配置端口,配置電壓可在3.3 V和2.5V兩者中選其一。P1是有源晶振,可提供FPGA系統(tǒng)時鐘頻率。RP1是打印機數(shù)據(jù)端口的上拉排阻,這樣輸出數(shù)據(jù)與端口數(shù)據(jù)邏輯與之后輸入打印機,避免顯示亂碼。打印機RD-E32-V8與FPGA由8根數(shù)據(jù)線和3條控制、狀態(tài)讀寫線連接,另有一條線將2部分的接地端連接到公共的模擬地線。

2 軟件實現(xiàn)

系統(tǒng)軟件設(shè)計是基于VHDL語言編寫的。軟件設(shè)計的關(guān)鍵是在打印機工作時序的基礎(chǔ)上完成微型打印機與FPGA之間數(shù)據(jù)和指令的讀寫和狀態(tài)的檢測。

2.1 控制時序與原理

控制過程的時序在延遲時間上有嚴格的要求,所以,設(shè)計控制程序時,必須考慮打印機狀態(tài)轉(zhuǎn)換和數(shù)據(jù)傳輸?shù)难舆t時間。當數(shù)據(jù)線上有待打印的數(shù)據(jù)時,打印機并不是立即將數(shù)據(jù)打印輸出,必須根據(jù)當前的打印機狀態(tài)來判斷。

當BUSY狀態(tài)被檢測到為“1”時,說明打印機處于“忙”狀態(tài),此時打印機不會接收任何數(shù)據(jù)。當BUSY信號為“O”時,說明打印機處于“空閑”狀態(tài),先向數(shù)據(jù)線寫入數(shù)據(jù),在延時時間符合時序的情況下,通過FPGA控制信號,將數(shù)據(jù)寫入打印機。為數(shù)據(jù)選通觸發(fā)脈沖,下降沿時輸入數(shù)據(jù),對低電平的時間時序上也有要求,最小為O.5μs。當下降沿到來的同時,數(shù)據(jù)即送入打印機,同時BUSY信號由低電平跳變?yōu)楦唠娖剑柚笷PGA向打印機數(shù)據(jù)線寫入數(shù)據(jù)。當數(shù)據(jù)輸入以后,直到回答脈沖跳變成低電平,此時表示數(shù)據(jù)已被接受,而且打印機準備好接受下一數(shù)據(jù),之后大約5μs時間以后,BUSY信號變?yōu)榈碗娖剑蠹s5μs信號變高。對打印機的控制是通過查詢方式實現(xiàn)的,根據(jù)打印機工作時序,將打印機控制過程分為3個狀態(tài),打印機控制程序基于這3個狀態(tài),采用VHDL語言的有限狀態(tài)機編寫實現(xiàn)。時序與狀態(tài)轉(zhuǎn)換如圖3所示。

評論