基于邏輯分析內核的FPGA電路內調試技術

隨著FPGA融入越來越多的能力,對有效調試工具的需求將變得至關重要。對內部可視能力的事前周密計劃將能使研制組采用正確的調試戰略,以更快完成他們的設計任務。

“我知道我的設計中存在一個問題,但我沒有很快找到問題所需要的內部可視能力。”由于缺乏足夠的內部可視能力,調試FPGA基系統可能會受挫。使用通常包含整個系統的較大FPGA時,調試的可視能力成為很大的問題。為獲得內部可視能力,設計工程師必須把一些引腳專門用作調試引腳,而不是實際用于設計。哪些工具可用于進行內部FPGA跡線測量?又有哪些技術可用固定的引腳數最大化內部可視能力?

FPGA設計工程師有兩種進行內部跡線測量的方法:

1. 把結點路由至引腳,使用傳統的外部邏輯分析儀測試。

2. 把一個邏輯分析儀內核插入FPGA 設計,通過JTAG把由內部FPGA存儲器保存的跡線捕獲路由輸出。

邏輯分析

FPGA開發者要在設計前期作出重要的判定,他們有意識或無意識地確定如何能夠調試他們的設計。得到內部FPGA可視能力的最常用方法是使用邏輯分析儀,把感興趣的內部結點路由至分析儀探測的引腳。這種方法提供深存儲器跡線,在這里問題成因和其影響可能有很大的時間間隔。邏輯分析儀能很好測量可能逃逸仿真的異步事件。一個例子是具有非相關頻率的兩個或多個時鐘域交互影響。邏輯分析儀提供強大的觸發,所得到的測量結果能建立與其它系統事件的時間相關。

傳統邏輯分析儀提供狀態和定時模式,因此可同步或異步地捕獲數據。在定時模式,設計工程師能看到信號躍變間的關系。在狀態模式,設計工程師有能力觀察相對于狀態時鐘的總線。當調試總線值至關重要的數據路徑時,狀態模式是特別有用的。

有效的真實世界測量需要事先周密的計劃。使用傳統邏輯分析儀要顧及的主要權衡是把結點路由輸出至可探測的引腳。傳統邏輯分析儀只能觀察到路由至引腳的信號。由于還不知道潛在的電路內調試問題,設計工程師只能把很少幾個引腳用于調試。這樣少的引腳數可能不足以提供解決手頭問題的足夠可視能力,從而延誤項目的完成。

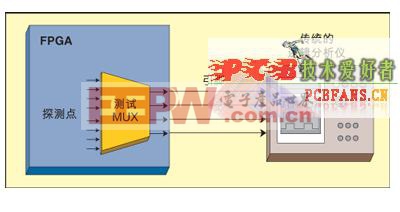

保持內部可視能力,同時減少專用于調試引腳數的一種方法是在設計中插入開關多路轉換器(見圖1)。例如當 FPGA 設計進入電路時,可能需要觀察128個內部結點,這就需要一次跟蹤32個通道。在這種情況下,可在FPGA設計中實現多路轉換器,在給定時間內路由出32 個結點。為編程多路轉換器,設計工程師可下載新的配置文件,使用JTAG或通過多路轉換器上的控制線經路由切換各信號。在設計階段,必須仔細規劃測試多路轉換器插入。否則設計工程師可能止步于不能同時訪問需要調試的結點。

Agilent 16702B所捕獲的跡線

圖1: 測試多路轉換器的插入使設計工程師有能力路由出內部信號的子集,圖中為Agilent 16702B所捕獲的跡線。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論