基于FPGA的CCD相機時序發生器的設計

FPGA-現場可編程門陣列技術是二十年前出現,而在近幾年快速發展的可編程邏輯器件技術。這種基于EDA技術的芯片正在成為電子系統設計的主流。大規模可編程邏輯器件FPGA是當今應用最廣泛的可編程專用集成電路(ASIC)。設計人員利用它可以在辦公室或實驗室里設計出所需的專用集成電路,從而大大縮短了產品上市時間,降低了開發成本。此外,FPGA還具有靜態可重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改。因此,FPGA技術的應用前景非常廣闊。

XC2VP20-FF1152 是Xilinx 公司推出的Virtex-II Pro 系列的FPGA,它內部有豐富的資源[5],包括8 個數字時鐘管理器(DCM),290Kbits 的分布RAM,88×16kByte 的Block RAM,88 個18×18 的專用乘法器(Dedicated Multipliers)單元,2 個PowerPC405 內核,564 個可配置I/O 引腳達(最多276 對差分I/O,速度高達3.125Gbps),最高內部工作頻率420MHz。

4.2 基于FPGA的科學級CCD相機時序發生器的設計與仿真

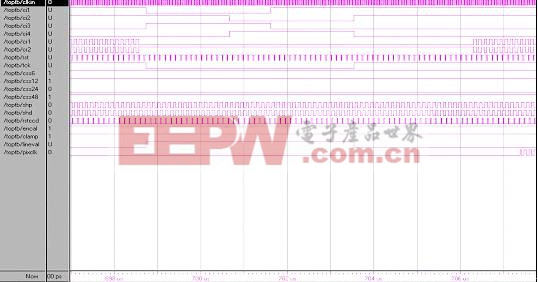

IL-E2型TDI-CCD的像元數有每行512,1024和2048三種,本文以2048像元數為例設計時序電路。2048為有效像元數,由于每行有5個隔離像元,4個暗參考像元,故設計中要保證最少使每行輸出2057個像元,也就是使每個行周期內最少有2057個CR1、CR2、RST驅動脈沖。每行除了2057個像元驅動脈沖以外,其余為空驅動脈沖。空驅動脈沖數越多,行周期時間越長,CCD曝光積分時間越長,靈敏度相應提高,但過長的曝光積分時間會使CCD輸出飽和失真,故空驅動脈沖數目不易過多。積分時間和像元移位讀出時鐘頻率是CCD時序電路的設計依據。在工程應用中,我們根據技術指標要求,算出行積分時間即行周期(T)為0.365ms,以此確定合適的系統主時鐘。驅動時序用超高速集成電路硬件描述語言(VHDL)編寫,程序主要包括:(1)調用所需的庫函數和程序包;(2)定義輸入和輸出端口;(3)用計數器對輸入的系統主時鐘進行分頻。(4)驅動時序信號的產生和輸出。由XILINX公司的設計軟件ISE6.2對XC2VP20-FF1152器件進行時序設計,通過時序仿真與工程應用驗證了能完成上述所有功能。系統邏輯功能時序仿真波形如圖4所示

圖4時序發生器時序仿真圖

5 結束語

本文的創新是采用FPGA 器件設計科學級CCD相機時序發生器, 使得電路由原來復雜的設計變成主要只用一片XILINX公司的可編程器件XC2VP20-FF1152來實現。獨立的單元測試與系統聯調結果均表明: 采用現場可編程門陣列(FPGA) 技術實現CCD相機時序發生器, 可使電路成倍簡化,提高了系統的集成度,時序發生器抗干擾能力也增強了,其功耗也成倍降低,從而實現了科學級CCD 相機工作時的高可靠性、穩定性,同時還使設計與調試周期成倍縮短。該設計方案為TDI-CCD在科學級CCD相機中的應用開拓了更加廣闊的前景。

評論