基于FPGA的多級小波逆變換實時系統設計

2.3 核心計算單元ILWC設計

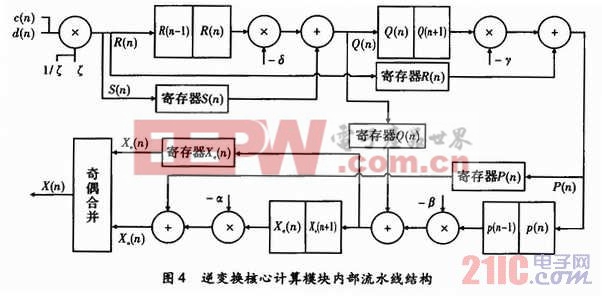

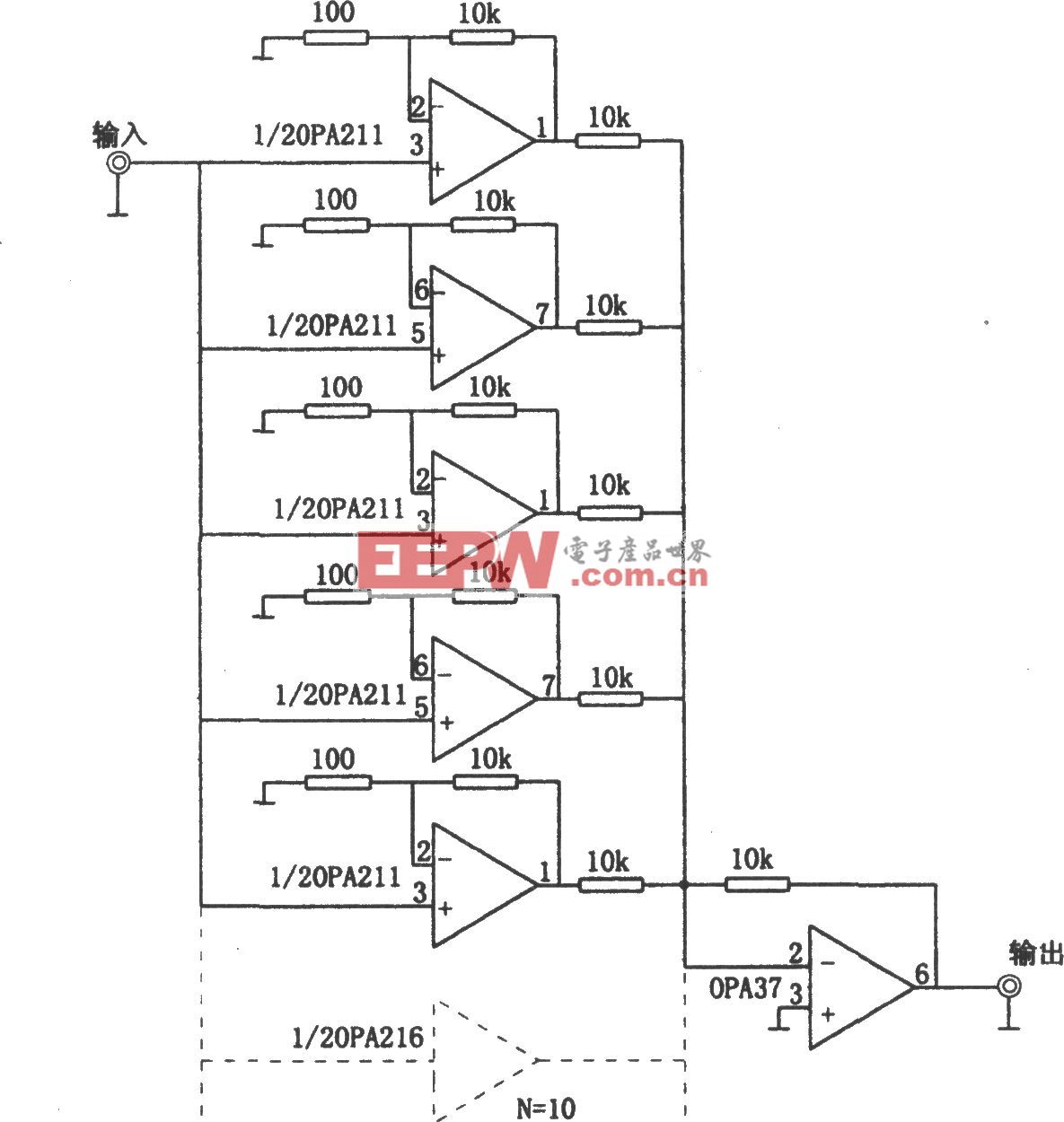

由圖4所示,核心計算單元對高低頻系數的伸縮擴展共用一個乘法器,因此平均每個小波系數所需進行的乘法和加法次數分別為5次和8次,相對于卷積運算的9次和14次,計算復雜度顯然是降低了很多。

3 軟件及硬件資源的選用

3.1 工作環境

本設計基于Xilinx公司ISE 9.1開發平臺之上,使用VHDL語言(93版本)編程實現。系統采用Synplify8.1進行綜合,使用Modelsim SE 6.0d進行仿真驗證。在沒有添加任何約束的情況下,其性能參數如表1所示。

選用Virtex-Ⅱ系列的芯片原因在于:(1)軟件開發工具友好,開發容易,性價比高;(2)低功耗、低工作電壓,滿足實時設備的要求;(3)仿真可靠,幾乎完全接近實際情況;(4)可重復擦寫型FPGA,設計靈活,適用于方案改進。

3.2 實驗結果

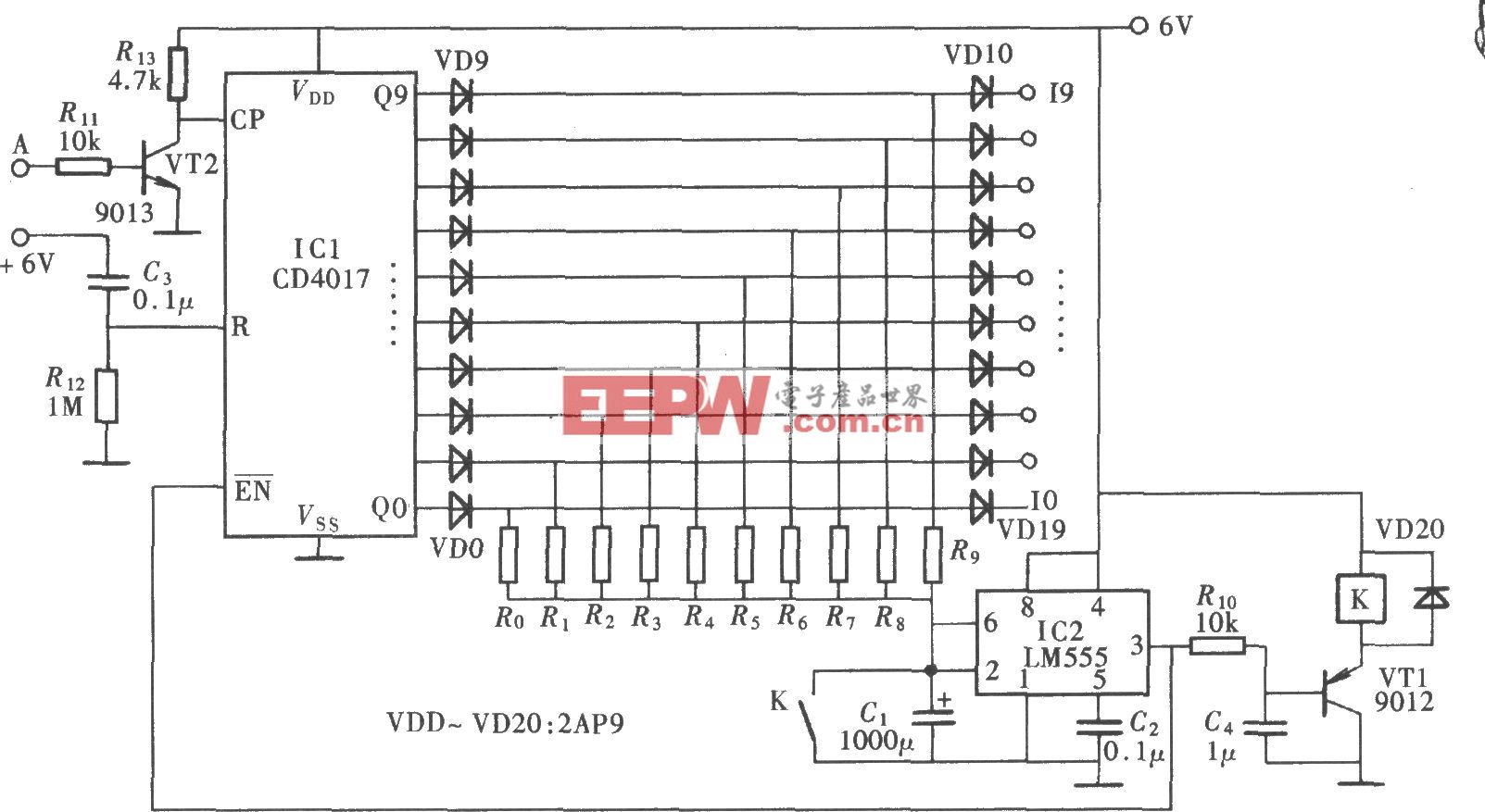

本系統采用8位64×4 096的原始圖像經過3層定點化小波處理所得的14位小波系數為測試數據,實驗處理結果與VC軟件定點化逆小波處理結果一致,表明本系統能正確的滿足應用要求,圖5為本系統工作整體仿真圖。系統在同步信號Syn低電平有效期間,根據切換信號Exg的高、低電平選擇片外存儲器進行乒乓操作。首先數據由Data輸入到片外存儲器,作為逆變換的測試數據,處理完成之后由Result端輸出,并以一個高電平脈沖信號Endn標記處理完畢。

4 結束語

本文討論下JPEG2000解碼系統中的CDF9/7小波逆變換模塊的設計要求,借助提升算法原位操作的特點,所提出的雙路并行的實時處理方案無需任何內部存儲空間,而外部存儲空間的大小完全取決于處理圖像塊尺寸的大小。在視頻及衛星遙感圖像這類實時性要求非常強的圖像處理中,本系統能很好地滿足應用需求。

評論