基于FPGA 的嵌入式塊SRAM 的設計

摘 要:文章中提出了一種應用于FPGA 的嵌入式可配置雙端口的塊存儲器。該存儲器包括與其他電路的布線接口、可配置邏輯、可配置譯碼、高速讀寫電路。在編程狀態下,可對所有存儲單元進行清零,且編程后為兩端口獨立的雙端存儲器。當與FPGA 其他邏輯塊編程連接時,能實現FIFO 等功能。基于2.5V 電源電壓、chart 0.22μm CMOS 單多晶五鋁工藝設計生產,流片結果表明滿足最高工作頻率200MHz,可實現不同位數存儲器功能。

1 引言

對于邏輯芯片的嵌入存儲器來說,嵌入式SRAM 是最常用的一種,其典型的應用包括片上緩沖器、高速緩沖存儲器、寄存器堆等。除非用到某些特殊的結構,標準的六管單元(6T)SRAM 對于邏輯工藝有著很好的兼容性。對于小于2Mb 存儲器的應用,嵌入式SRAM 可能有更好的成本效率并通常首先考慮。

Xilinx 公司SRAM型FPGA 主要由配置存儲器、布線資源、可編程I/O、可編程邏輯單元CLB、塊存儲器BRAM 和數字時鐘管理模塊組成。它包含了分布式RAM,位于CLB中。每個CLB包含了16 × 1bit的SRAM結構。BRAM的加入既增加了RAM的容量,也可構成大型LUT,更完善了CLB 的功能。

2 BRAM塊劃分

現代數字系統對存儲器容量的存儲速率要求越來越高,讀訪問時間就是一個重要參數,它是從地址信號的出現到存儲在該地址上的數據在輸出端出現的時間延遲。提高BRAM 讀取速度的一個有效辦法是減小位線和字線上的總負載電容,這可以通過減少連接在同一字線和位線上的存儲單元數目來實現,即采用存儲陣列分塊技術。本電路采用設計多個BRAM的方法,每個BRAM都有自己的譯碼電路、敏感放大器和數據通道,各個BRAM 獨立工作,每個BRAM 的讀取時間得到了大大提高。

3 BRAM塊設計

3.1 BRAM與布線資源接口

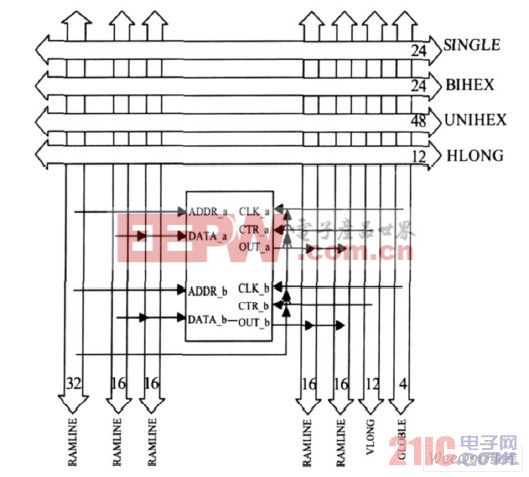

FPGA 中每個BRAM塊都嵌在內部連線結構中,與BRAM 直接相連的有RAMLINE、VLONG 和GLOBAL。左邊32根RAMLINE提供BRAM的地址輸入,也可以提供控制信號(CLK、WE、ENA、RST)的輸入。左邊兩組16 根RAMLINE 一起布線提供BRAM雙端口的數據輸入,右邊兩組RAMLINE提供BRAM雙端口數據輸出通道。4 根GLOBLE全局時鐘線優化用作時鐘輸入,提供較短的延遲和最小的失真。VLONG也被專門用作BRAM中WE、ENA、RST的控制輸入。RAMLINE 為BRAM專有布線,如從水平方向的SINGLE、UNIHEX、BIHEX通過可編程開關矩陣PSM 把信號輸送到RAMLINE 上,進而送到BRAM 用作地址、數據。而BRAM 的輸出也通過RAMLINE最終送到HLONG上。

圖1 BRAM周圍布線

相鄰BRAM 的RAMLINE 也可通過三態門連到下一級的RAMLINE,于是整列中的BRAM 可共享RAMLINE 上的數據。每個BRAM與FPGA其他電路的相連主要通過水平方向的4 組主要互連線完成。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論