用CPLD和Flash實現FPGA配置

2 具體設計

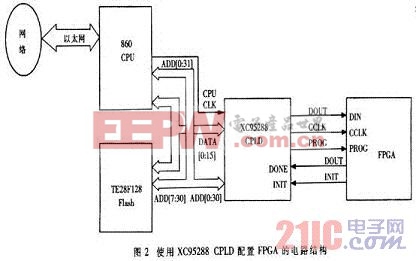

國家數字交換系統工程技術研究中心承擔的國家863項目高性能IPv6核心路由器采用一片Intel E28F128J3A150 16位Flash作為BootFlash對PowerPC2860(MPC860)處理機進行加電配置下載更新的方案,其多余的存儲空間完全可以存放下FPGA所需的配置文件。加電復位、系統啟動后,由處理機與一片XilinxXC95288XL CPLD配合,控制FPGA配置文件從Flash下載到FPGA中,完成對FPGA的配置。860處理機支持網絡功能,當配置文件需要更新時,可通過網絡將新的配置文件發送到處理機,然后再由處理機更新系統中的Flash。采用XC95288CPLD配置FPGA的具體電路設計結構如圖2所示。本文引用地址:http://www.104case.com/article/191336.htm

圖2中,CPLD主要功能是把從Flash中讀出的數據轉換成串行輸出,然后再將地址遞增。CCLK(信號由CPU時鐘產生。PROG信號則由CPU輸出的地址數據經譯碼模塊產生。XC95288C PLD邏輯結構如圖3所示。

下面分別介紹各功能模塊的具體實現:

(1)數據轉換成串行輸出功能模塊:使用了一個右移寄存器。從16位Flash來的并行數據DIN[0:15]加載到移位寄存器后,依次從DOUT串行輸出到FPGA中。

(2)地址遞增功能模塊:此功能由兩個計數器完成。由于Flash是16位并行數據端口,因此第一個計數器功能是逢16進1,第二個計數器功能是Flash地址遞增。當移位寄存器的16位數據都輸出到FPGA中后,第一個計數器輸出端口CNT[0:3]都為“1”,經過“與門”邏輯使得第二個計數器加l。Intel E28F128J3A150 Flash為16MB,共需要25根地址線。由于Flash是16位的,因此ADD[3l]不連接。所以第二個計數器和地址線ADD[7:30]相連.以完成Flash地址的遞增。

(3)CCLK信號產生模塊:CPU來的時鐘信號將數據信號DOUT輸出,經一個“非門”邏輯延遲半個周期后產生CCLK,CCLK再將DOUT上的數據送到FPGA中。這樣將讀寫。DOUT數據的時刻叉開,避免了沖突。

(4)PROG信號產生模塊:當需要下載FPGA程序時,由CPU產生一個地址信號ADD[O:30],經譯碼器譯碼產牛PROG控制信號。此地址由用戶自行設定。

以上模塊均采用VHDL語言描述。數據轉換成串行輸出功能模塊是核心部分,它可實現并行數據串行輸出。

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。與傳統的JTAG或PROM串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、適用于大容量FPGA下載的特點。采用此方法可以不用打開機箱即可隨時更新FPGA配置程序,特別適用于需要不斷更新的系統設計中,具有較為廣闊的應用前景

評論