用CPLD和Flash實現FPGA配置

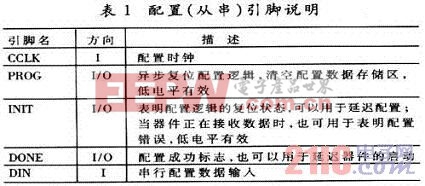

主、從模式的最大區別在于:主模式的下載同步時鐘(CCLK)由FPGA提供;從模式的下載同步時鐘(CCLK)由外部時鐘源或者外部控制信號提供。主模式對下載時序的要求比從模式嚴格得多。因此從處理機易于控制下載過程的角度考慮,選擇使用從串模式或從并模式較為合適。本設計采用從串模式進行FPGA配置。從串模式引腳說明如表l所示。

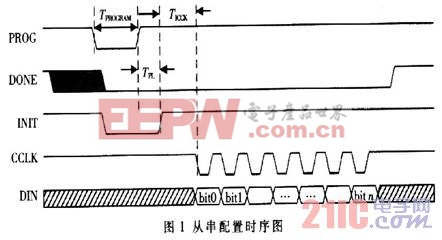

從串配置時序圖如圖l所示。TPROGRAM是配置邏輯的復位時間,對xilinx VIRTEXE和VIRTEX2系列,最小應大于300ns。TPL為復位延遲時問,表明配置邏輯復位的延續。對VIRTEXE系列來說,當復位信號PROG變為高電平時,INIT立即變為高電平,配置邏輯就可以接收配置數據流;而對于VIRTEX2系列,TPL最小有500ns的延遲。TICCK為配置時鐘CCLK的輸出延遲。

當PROG有效(對配置邏輯進行復位)時,FPGA將置低INIT和DONE;PROG變為高電平時,INIT將延遲一段時間用于表明復位狀態的延續,繼續置低INIT可以延遲配置的進行。當FPGA正在接收配置數據時,INIT變低,表明CRC校驗錯。當配置完所有的數據時,若配置正確,DONE將會變高。此后FPGA開始啟動序列,繼續置低DONE可以延遲啟動的進行。

評論