基于FPGA的FFT算法硬件實現

2 系統仿真結果

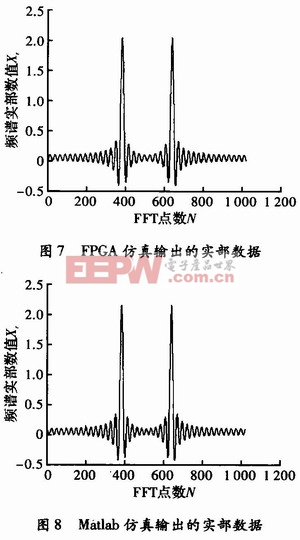

輸入數據為s=1 024×cos(2π×f_in×t),其中f_in=50 M,Fs=80 MHz,n=40,t=0:1/Fs:(n-1)/Fs,利用QuartusⅡ軟件對系統在100 MHz的時鐘環境下進行了仿真,將仿真輸出結果轉換成tbl文件并利用Matlab軟件讀取后,得到如圖7所示的頻譜數據圖(實部數據部分)。本文引用地址:http://www.104case.com/article/191332.htm

圖8所示為Maflab自帶FFT函數對于輸入相同1 024點數據的FFT計算結果(同樣為實部數據部分)。

通過比較可以看到,本設計的仿真結果與Matlab的仿真結果基本一致,可以正確高效地計算出1 024點FFT數據。

3 結束語

本設計全部由Verilog HDL語言實現,采用自頂向下的設計方法,完成了一種基于FPGA的1 024點16位FFT算法,共需要5級運算,每級需要計算256個蝶形。提出了將蝶形運算先進行前一級的蝶形加減運算,再進行本級的與旋轉因子復乘運算的結構。由前所述,平均每個蝶形運算需要4個時鐘周期,所以理論上完成1 024點FFT的總時鐘周期為N=256×4×5=5 120;假設使用的時鐘為100MHz,那么將耗時T=5 120×(1/100)=51.2μs,這與仿真結果51.32μs基本一致。

評論