基于FPGA的數字示波器

4 系統(tǒng)測試分析

(1)單次觸發(fā)掃描測試,觀察設計的示波器能否產生掃描電壓,并在信號上升沿開始顯示波形。觀察結果能夠產生掃描電壓,并顯示波形。

(2)經測量得到輸入短路時輸出噪聲的峰-峰值為1.72 mV。

(3)100 kHz方波校準信號的電壓幅值為0.308 V,誤差為0.69%。

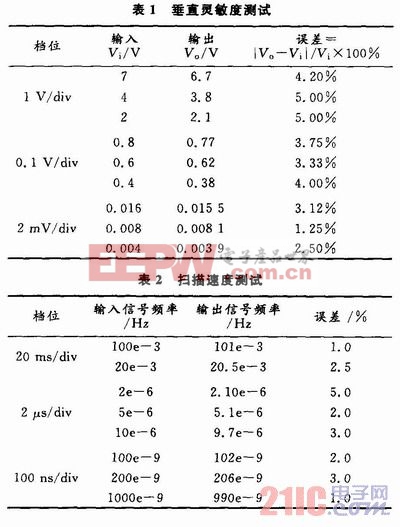

(4)垂直靈敏度測試。正弦信號頻率為10 kHz,記錄數據如表1所示。

由表2中數據可知,測量結果都在測量誤差允許范圍內,很好地完成了設計任務。

5 結語

該系統(tǒng)的突出特點采用FPGA作為核心控制器,同時結合NIOS軟核的優(yōu)勢,實現了數字示波器的設計。結果表明,系統(tǒng)總體功能完善,集成度高,全數字化,體積小,重量輕,可靠性高,易于程控,使用靈活。

評論