基于FPGA的數字示波器

2.2 采樣分析及A/D數據采集電路

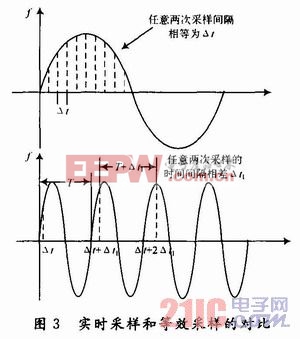

對于信號的采樣分為兩種方法,實時采樣和等效采樣。實時取樣對波形進行等時間間隔取樣,按照取樣先后的次序進行A/D轉換,并存入存儲器中。等效時間取樣方式是先采用“取樣技術”,將周期性的高頻信號變換成波形與其相似的周期性低頻信號,然后再做進一步的處理,因而可以比較容易地獲得很寬的頻帶寬度。但等效時間取樣僅限于處理重復性的周期信號。圖3是實時采樣和等效采樣的對比。本文引用地址:http://www.104case.com/article/191331.htm

由于系統的最高時鐘為50MHz,綜合以上考慮和現實要求,該系統采用了等效采樣和實時采樣兩種采樣方式。當輸入信號頻率低于10M-Hz,選用實時采樣;反之,選用等效采樣。數據采集電路中AD芯片選用TI公司的ADS830E,它是一個單通道并行8位的模/數轉換器,采樣速率最高可達60 MHz。為了減少硬件電路的設計和消除其他信號的干擾,A/D數據采集中的采樣時鐘由FPGA提供。

2.3 單片機控制模塊設計

單片機控制模塊采用TI公司的MSP430F149單片機。MSP430F149控制信號調理模塊以及按鍵的輸入等。

2.4 系統中FPGA設計

2.4.1 時鐘分頻電路設計

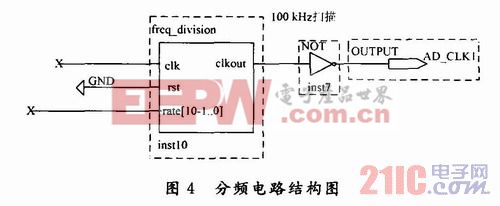

該數據采集系統具有比較寬的測量范圍,在FPGA內部設計了一個分頻電路,用來實現針對不同頻率的被測信號選擇不同的采樣頻率,確保采集數據更加精確。圖4是使用Verilog實現的分頻電路,該電路可以實現對50 MHz頻率的時鐘源進行分頻。分頻比可由程序控制,從而使時鐘滿足A/D采集的需求。

評論