基于FPGA和DDS技術(shù)的任意波形發(fā)生器設(shè)計

摘要:根據(jù)現(xiàn)代電子系統(tǒng)對信號源的頻率穩(wěn)定度、準(zhǔn)確度及分辨率越來越高的要求,結(jié)合直接數(shù)字式頻率合成器(DDS)的優(yōu)點,利用FPGA芯片的可編程性和實現(xiàn)方案易改動的特點,提出了一種基于FPGA和DDS技術(shù)的任意波形發(fā)生器設(shè)計方案。采用VHDL和原理圖輸入方式,在Quar-tusⅡ平臺下實現(xiàn)該設(shè)計的綜合和仿真,用Matlab對仿真數(shù)據(jù)進(jìn)行處理及顯示,驗證了設(shè)計的正確性。通過設(shè)置參數(shù)可以靈活控制輸出頻率和分辨率。

關(guān)鍵詞:DDS;FPGA;波形發(fā)生器;VHDL

0 引言

隨著現(xiàn)代電子技術(shù)的發(fā)展,在通訊、雷達(dá)、宇航、電視廣播、遙控遙測和電子測量等使用領(lǐng)域,對信號源的頻率穩(wěn)定度、頻譜純度、范圍和輸出頻率提出了越來越高的要求。為了提高頻率穩(wěn)定度,經(jīng)常采用晶體振蕩器等方法來解決,但已不能滿足眾多應(yīng)用場合的要求。伴隨電子測量技能與計算機(jī)技能的緊密結(jié)合,一種新的信號發(fā)生器——任意波形發(fā)生器應(yīng)運而生,它可產(chǎn)生由用戶定義的任意復(fù)雜的波形,因而具有廣闊的運用發(fā)展前景。目前設(shè)計波形發(fā)生器的要領(lǐng)通常有三種:

(1)傳統(tǒng)的直接頻率合成技能(DS)。該類要領(lǐng)能實現(xiàn)高速頻率變換,具有低相位噪聲以及所有要領(lǐng)中最高的工作頻率。但由于采用大量的倍頻、分頻、混頻和濾波環(huán)節(jié),導(dǎo)致其結(jié)構(gòu)復(fù)雜、體積龐大、成本昂貴,而且容易產(chǎn)生過多的雜散分量。

(2)鎖相環(huán)式頻率合成器(PLL)。該類技能具有良好窄帶跟蹤特征,可選擇所需頻率信號,抑制雜散分量,且省去大量濾波器,有利于集成化和小型化。但由于鎖相環(huán)本身是個惰性環(huán)節(jié),鎖定時間較長,因而頻率轉(zhuǎn)換時間較長,且由模擬要領(lǐng)合成的正弦波參數(shù)(如幅度、頻率和相位等)都難以定量控制。

(3)直接數(shù)字式頻率合成器(direct digital frequency,DDS)。該類要領(lǐng)具有高頻率穩(wěn)定度、高頻率分辨率以及極短的頻率轉(zhuǎn)換時間。此外,全數(shù)字化結(jié)構(gòu)便于集成,輸出相位連續(xù),頻率、相位和幅度均可實現(xiàn)程控,而且理論上能夠?qū)崿F(xiàn)任意波形。

鑒于DDS技術(shù)的優(yōu)點,本文利用FPGA芯片的可編程性和實現(xiàn)方案易改動的特點,提出一種基于FPGA和DDS技術(shù)的任意波形發(fā)生器設(shè)計新方法。

1 DDS的基本原理

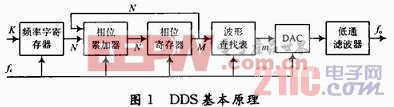

DDS的基本原理是利用采樣定理,通過查表法產(chǎn)生波形。DDS的結(jié)構(gòu)有很多種,其基本的電路原理可用圖1來表示。

DDS是從相位概念出發(fā),直接對參考正弦信號進(jìn)行抽樣,得到不同的相位,通過數(shù)字計算技術(shù)產(chǎn)生對應(yīng)的電壓幅度,最后濾波平滑輸出所需頻率。下面通過從相位出發(fā)的正弦函數(shù)產(chǎn)生描述DDS的概念。

圖1中,K為頻率控制字;N為相位累加器的字長;M為ROM地址線位數(shù);m為ROM數(shù)據(jù)線位數(shù),即DAC的位數(shù);fc為DDS系統(tǒng)的參考時鐘源,通常是一個具有高穩(wěn)定性的晶體振蕩器,為整個系統(tǒng)的各個組成部分提供同步時鐘。

DDS的數(shù)學(xué)模型可歸結(jié)為:在每一個時鐘周期T內(nèi),頻率控制字K與N比特相位累加器累加1次,同時對2N取模運算,得到的和(以N位二進(jìn)制數(shù)表示)作為相位值,以二進(jìn)制代碼的形式查詢正弦函數(shù)表ROM,再將相位信息轉(zhuǎn)變成相應(yīng)的數(shù)字量化正弦幅度值。ROM輸出的數(shù)字正弦波序列經(jīng)數(shù)/模轉(zhuǎn)換器轉(zhuǎn)變?yōu)殡A梯模擬信號,最后通過低通濾波器平滑后得到一個純凈的正弦模擬信號,其頻率為:![]()

相位累加器由N位加法器與N位累加寄存器級聯(lián)構(gòu)成。每來一個時鐘脈沖fc,加法器將頻率控制字K與累加寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的結(jié)果送至累加寄存器的數(shù)據(jù)輸入端。累加寄存器將加法器在上一個時鐘脈沖作用后所產(chǎn)生的新相位數(shù)據(jù)反饋到加法器的輸入端,以使加法器在下一個時鐘脈沖的作用下繼續(xù)與頻率控制字相加。這樣,相位累加器在時鐘作用下,不斷對頻率控制字進(jìn)行線性相位累加。由此可以看出,相位累加器在每一個時鐘脈沖輸入時,把頻率控制字累加1次,相位累加器輸出的數(shù)據(jù)就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號頻率。用相位累加器輸出的數(shù)據(jù)作為波形存儲器(ROM)的相位取樣地址,這樣就可把存儲在波形存儲器內(nèi)的波形抽樣值(二進(jìn)制編碼)經(jīng)查找表查出,完成相位到幅值轉(zhuǎn)換。波形存儲器的輸出送到D/A轉(zhuǎn)換器,D/A轉(zhuǎn)換器將數(shù)字量形式的波形幅值轉(zhuǎn)換成所要求合成頻率的模擬量形式信號。低通濾波器用于濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號。

評論