基于FPGA 的衛星便攜站的同步數字復接器的設計

1. 2. 3 分接器

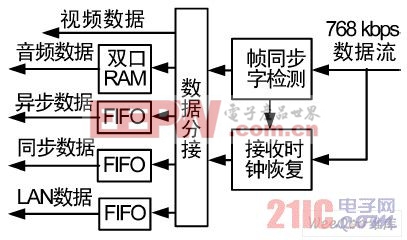

分接器負責將一路數據流分解成各個支路信息數據。它包括數據分接電路、時鐘恢復電路、數據接收存貯器和數據緩沖單元等部分。時鐘恢復電路產生解幀所需的各種時鐘和相應的支路時隙,這些時鐘和接口接收的數據一起送入數據分接電路,搜索幀同步字,當滿足同步規則后判為同步,同時強迫時序與數據幀同步對應,將各支路信息數據分接,并送相應的解碼單元,不同步給出同步/ 失步告警信號;數據接收存貯器為一雙口RAM,用來發送數字音頻數據; 數據緩沖單元用來把分接的同步數據的相位調整到滿足數據接口的相位。復接器的組成框圖如圖3 所示。

圖3 分接器組成框圖

1. 2. 4 幀同步字檢測

對于集中幀同步字方式,幀同步字在數據流中是若干個連續的碼元,占據相鄰的時隙,因此幀碼檢測電路比較簡單,可由位數等于幀碼個數的D 觸發器和與門構成。數據由時鐘逐位打入D 觸發器中,一旦12 位幀碼都移入D 觸發器中,即12 個D 觸發器輸出為幀同步字,則與門輸出一個脈沖,否則與門沒有輸出。為防止假同步,連續3 次搜索到幀同步字才認為設備同步,否則重新搜索。當信道誤碼率較高時,為避免設備頻繁失步,當連續3 次失步才認為設備失步。

采用上述方法既可以防止假鎖,又可以避免啟動不必要的同步搜索,使設備工作更加穩定可靠。

所有以上功能除接口轉換及時鐘鎖相外,全部使用FPGA 器件,采用硬件設計語言實現。并按功能模塊化設計,具有很好的重用性,可以方便地進行移植。

1. 2. 5 仿真與實現

該復接器是在Altera 公司的QuartusII5. 1 作為硬件開發平臺,完全采用VHDL 硬件描述語言編寫,并在QuartusII5. 1 的開發環境下進行時序仿真,系統仿真波形良好,除了允許范圍內的信號延遲外,能準確實現數字信號的復接和分接,經過編譯下載到可編程器件中,程序已通過了綜合實驗,獲得很好的效果,滿足了工程的需要。

2 系統同步性能分析

在傳輸過程中,由于信道噪聲的影響,不可避免地將在傳輸碼流中引入誤碼,從而導致系統同步的丟失。同步丟失是一個非常嚴重的問題,它將導致主觀質量的嚴重下降,甚至使得整個系統不能正常工作。因此,復分接系統同步性能的好壞,是影響整個系統性能的關鍵環節。

在發送端,復分接系統輸出數據流幀長為L =7 680 bit。在每幀的起始,是固定數值的同步幀頭,碼長為N = 12 bit,根據文獻[ 3] ,有平均搜捕時間:

式( 3) 中,P 1 為同步字上的虛漏概率; Py 為非同步字上的虛警概率; T 為數據幀周期。如果信道的平均比特誤碼率 ,傳送流的速率R =768 kbit / s,那么P1 = NP = 0. 001 2,P y = 2-12=0. 000 2, T = L / R, 于是Ta = 12. 68 ms。

,傳送流的速率R =768 kbit / s,那么P1 = NP = 0. 001 2,P y = 2-12=0. 000 2, T = L / R, 于是Ta = 12. 68 ms。

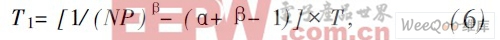

如果不考慮虛警概率的影響,平均確認失幀時間為:

式( 4) 中,β為后向保護參數,即在連續β次發現同步字丟失后才進入失步狀態。取β = 3,那么Td= 25 ms。另外,平均失幀時間為:

式( 5) 中,a為前向保護參數,即在連續a次找到同步字后才進入同步狀態。a= 3,那么Tr = 50 ms。而平均同步持續時間為:

所以T1= 1 607 h。從上面的分析中可以看出復分接系統即使在不進行誤碼保護的情況下,也能在較短的時間內確認失幀,并很快搜捕到同步; 同時在同步狀態保持很長的時間。因此,該復分接系統具有較好的同步性能,在一定的誤碼保護措施下能夠滿足實際要求。

3 結束語

設計的數字復接系統的各個部分,都可以在FPGA 芯片上用VHDL 編程實現。整個復分接系統功能就可以集成在一塊芯片上,既節省了硬件資源,減少外部走線,簡化了系統,而且該設計便于擴展,方便反復編寫和修改程序,只需修改FPGA 中相應控制參數和外接的監控信息就可以實現速率可變和幀結構可變的復接與分接。實驗表明,該系統在FDMA 便攜式衛星傳輸平臺中起到了重要作用,可提高信道的利用率和傳輸容量。

評論