一種基于FPGA 的嵌入式塊SRAM 的設(shè)計

3.2.1 可配置數(shù)據(jù)位寬實現(xiàn)方法

配置邏輯中三位控制信號WIDTH_SEL0∶2>連到BRAM中,同時對地址寬度、數(shù)據(jù)寬度進行控制。

由于BRAM可以實現(xiàn)1、2、4、8、16 位的任意位寬,所以地址總線寬度、數(shù)據(jù)總線寬度都必須滿足其中任意一種模式下的要求。于是設(shè)計時使地址總線寬度為各種模式下的最大值,即1位時的地址寬度11∶0>,其他模式下可使不用的地址位使能無效,進而獲得所需的地址位。數(shù)據(jù)總線寬度也設(shè)置為各種情況下的最大值,即16 位時的數(shù)據(jù)寬度15∶0>,其他情況下選擇有用的數(shù)據(jù)位進行存儲。

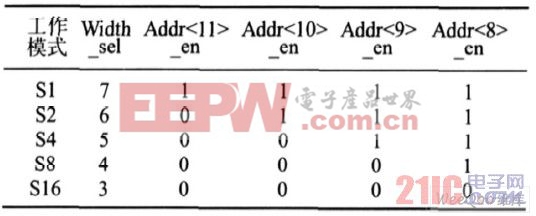

表1可見WIDTH_SEL0∶2>對地址使能的控制,主要在于對地址11∶8>的控制,其他位地址7∶0>則一直有效。

表1 不同數(shù)據(jù)位寬的地址使能

由WIDTH_SEL0∶2>另外譯碼產(chǎn)生一組數(shù)據(jù)控制信號,分別為S_1、S_2、S_4、S_8、S_16 控制數(shù)據(jù)如何分配到位線上。這當中* 根位線實行了分片,每片4 根:

S_1有效:DI0>可分配到16片中的任何一片上。

S_2有效:DI0∶1>可分配到0∶1>、2∶3>、4∶5>?任何相鄰兩片上,每片1 位數(shù)據(jù)。

S_4有效:DI0∶3>可分配到0∶3>、4∶7>、8∶11>、12∶15>任何相鄰四片上,每片1 位數(shù)據(jù)。

S_8 有效:DI0∶7>可分配到0∶7>或8∶15> 8片上,每片1 位數(shù)據(jù)。

S_16 有效:DI0∶15>剛好分配到16片上,每片1 位數(shù)據(jù)。

至于上述究竟存儲到哪些片上以及具體存儲到片內(nèi)哪根位線上則由列譯碼控制。

3.2.2 譯碼控制

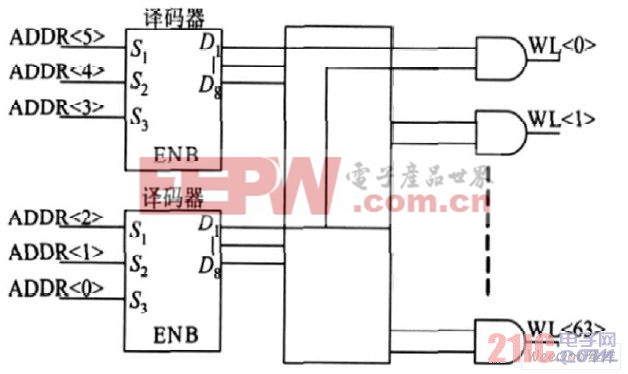

行譯碼采用了常用的3-8 譯碼器,3-8 譯碼器內(nèi)由與門組成。第一級用兩個3-8 譯碼器,輸入端接入行地址ADDR5∶0>,第二級用64 個與門把第一級譯碼進一步譯出來,可實現(xiàn)64 行中選出1 行。

圖2 64 選1 行譯碼

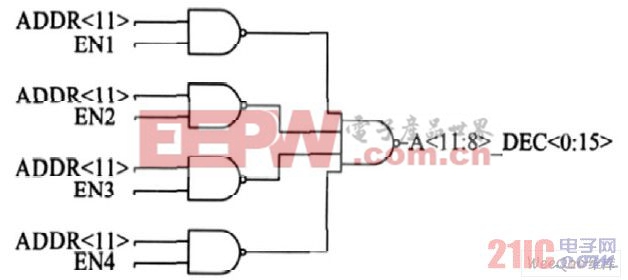

列譯碼相對較復雜,首先將列地址分為兩組,一組用于片選譯,一組用于片內(nèi)譯碼。片選地址由ADDR11∶8>組成,片內(nèi)譯碼由ADDR7∶6>組成。

片選地址譯碼由地址和地址使能組成,而地址使能則是由WIDTH_SEL0∶2>配置決定的。

圖3 片選譯碼

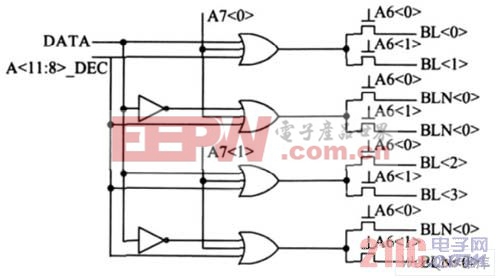

譯碼所得的A11∶8>_DEC0∶15>即可實現(xiàn)片選存儲。當配置為1 位時,4 位地址均有效,譯出的16位中只有1 位有效,只能選擇16 片中的1 片。當配置為2 位時,ADDR11>使能無效,譯出16位中有連續(xù)2 位有效,能選擇16 片中連續(xù)2 片。當配置為4 位時,譯出16 位中有連續(xù)4 位有效,能選擇16 片中連續(xù)4 片。配置為8 位就能選擇16 片中的上8 片或下8 片。配置為16 位,4 個地址均無效,譯出的16 位全有效,16 片全選。經(jīng)過了片選的一級譯碼,列譯碼還需經(jīng)過第二級的片內(nèi)譯碼。

圖4 片內(nèi)譯碼

評論