FPGA實現IRIG-B(DC)碼編碼和解碼的設計

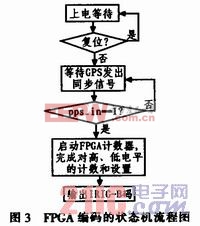

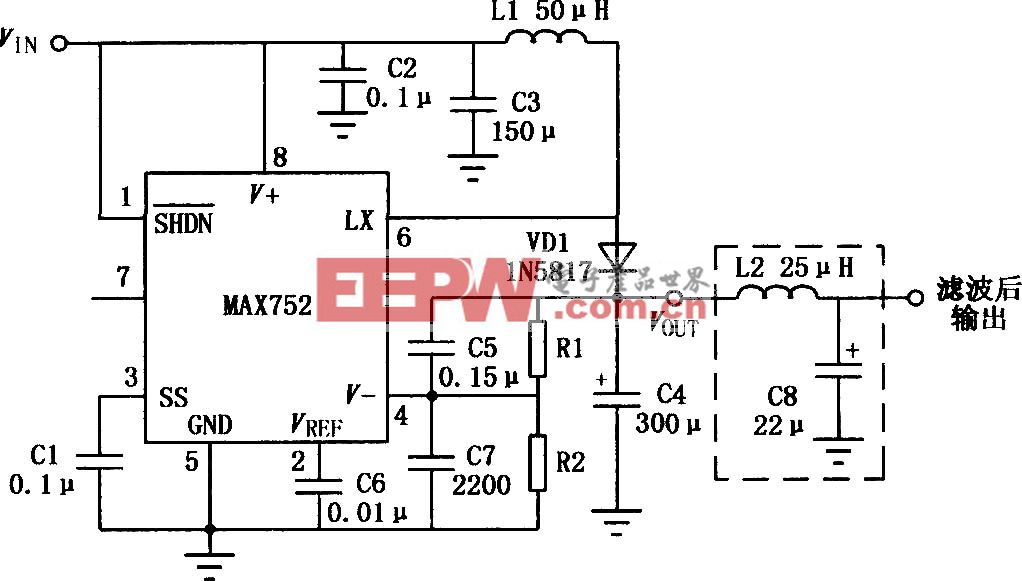

FPGA完成這個時刻的B碼編碼后,會立即不斷地搜索下一個pps_in的上升沿,GPS模塊每秒都會觸發pps_in的上升沿,一旦發現pps_in上升沿,馬上進入下一秒的編碼。這樣編程的好處是B碼大致上可以與1 pps同步,延遲少且方便測試。FPGA對IRIG-B碼秒信號的編碼仿真波形如圖4所示。

如上圖所示,第1行信號是40 MHz的晶振時鐘;第2行信號是輸入信號pps_in;第3行信號是復位信號,低電平有效;第4行信號是分頻后的時鐘信號5 MHz;第5行是輸入秒信號,此時秒信號sec bcd[7..0]為8位二進制數10001000;最后一行信號是B碼的編碼信號。當pps_in上升沿到來時,FPGA對B碼在5 MHz時鐘的上升沿處立即產生高電平,首先是B碼輸出位置識別標志Pr(高電平8 ms,低電平2 ms),接著8位二進制的秒信號從低位至高位輸出,實現計數器計數編碼,放大波形可以知道,此時B碼與pps_in有100 ns的滯后,100ns的延遲對時序同步影響很小,可以忽略不計。然后FPGA根據狀態機的狀態運行,直到下一個pps_in上升沿來臨。

3 IRIG-B碼解碼

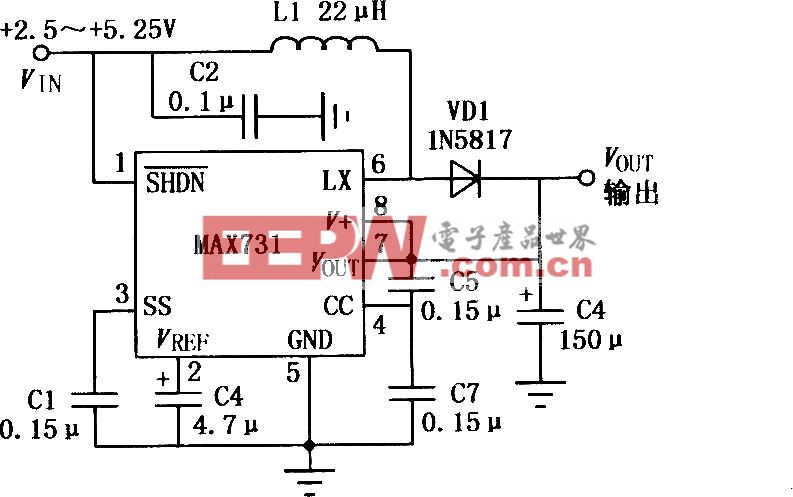

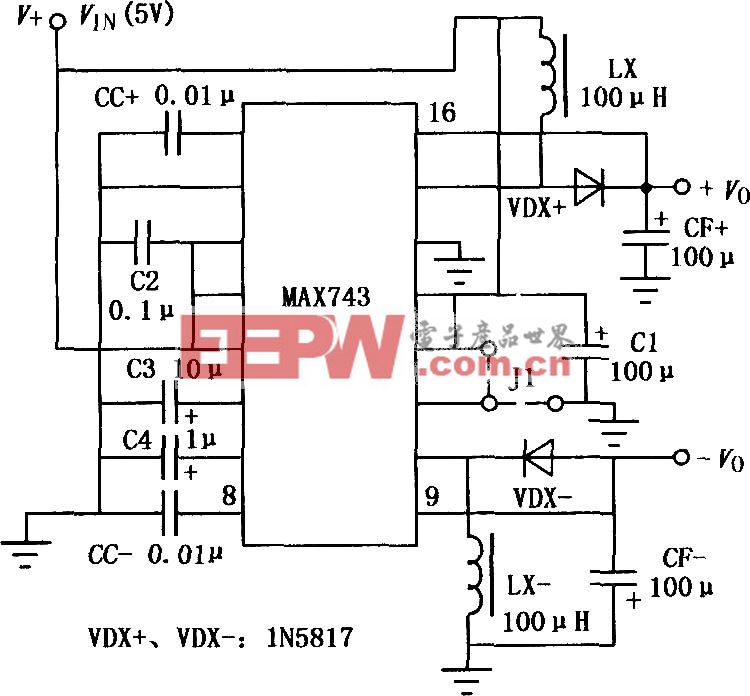

解碼部分的設計采用兩個時鐘來處理,晶振的時鐘為40 MHz,通過分頻,可以得到一個是10 kHz的時鐘,和一個10 MHz的時鐘。先采用10 kHz的時鐘,當連續監測到2個脈寬為8 ms的位置標示信號時,啟動1個計時器,當計時器計時到990 ms時,產生1個使能信號EN,這個信號是傳遞給高頻時鐘的監測使能信號。接著計時器清零,等待下一次監測到連續2個脈寬為8 ms的信號出現時,計時器重新開始計時。

如果只采用高頻時鐘的話,要監測2個脈寬為8 ms的信號與計時將會非常浪費邏輯資源。所以在前一部分的監測與計時用低頻時鐘進行;在準時對應的上升沿來臨前2 ms為高頻時鐘部分提供1個使能信號;高頻時鐘處理部分接收到此使能信號EN后再監測B碼的PR的上升沿,當監測到PR為高電平后,發出1個脈沖1 pps。經過這樣的處理,就能精確的提取出1 pps信號以及與1 pps精確同步的10 MHz脈沖信號。1 pps對時信號的提取如圖5所示。

評論