數字基帶傳輸系統的FPGA設計與實現

2.4 譯碼模塊的仿真

根據圖2所示,譯碼模塊方框圖在QuartusⅡ平臺上用VHDL語言編程,經編譯后可進行仿真。為了將譯碼結果與原始信號進行比較,將圖3,圖4的編碼結果作為譯碼器的輸入信號進行譯碼,將譯碼結果與以上的原始信號進行比較。

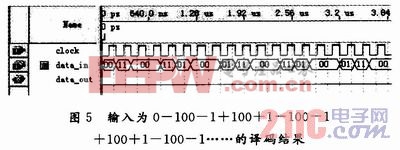

當輸入的HDB3碼為0-100-1+100+1-100-1+100+1-100-1+100+1……譯碼結果為全“0”碼,如圖5所示。圖中clock為時鐘信號,data_in為輸入HDB3碼,data_out為輸出的信碼。data_in為00,表示“0”電平;data_in為01,表示“+1”電平;data_in為11,表示“-1”電平。

將譯碼結果與編碼前的原始信號做比較,可看出兩者是一致的。本文引用地址:http://www.104case.com/article/191307.htm

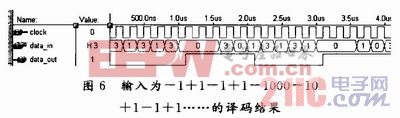

讓輸入信號data_in為31313000301313100010……,譯碼的結果為11111000001111100000……,如圖6所示。

將譯碼結果與編碼前的原始信號做比較,可看出兩者仍是一致的。

3 數字基帶系統設計與仿真

3.1 數字基帶系統的設計

HDB3編譯碼數字基帶系統的設計是在QuartusⅡ平臺上,采用原理圖的方式來實現的。首先,分別創建HDB3編碼模塊和譯碼模塊符號文件;然后新建基帶系統頂層文件;再在頂層文件中分別調入HDB3編碼模塊和譯碼模塊符號文件;按要求連線后,即得到HDB3編譯碼數字基帶系統電路。

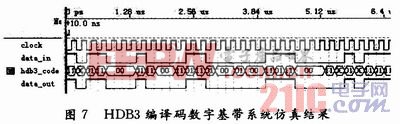

3.2 數字基帶系統的仿真

將以上原理圖進行編譯后,即可進行仿真。使輸入信碼為10110001000011000000111000001011,系統傳輸結果如圖7所示。圖中,clock為時鐘信號,data_in為輸入信碼,hdb3_code為系統傳輸用的HDB3碼,da_ta_out為輸出信碼。由圖可知,系統的輸出與輸入完全一致。

3.3 數字基帶系統的調試

當整個系統通過程序仿真后,將程序下載到ACEX1K-EP1K30TC144-1芯片,從而完成整個數字基帶系統的設計。調試時把發送部分與接收部分連接起來進行系統調試,檢測各測試點信號是否正確,在調試中,硬軟件要結合起來。由于芯片可以高度集成,問題一般出現在軟件上,故在調試中軟件參數的更改是最重要的。

4 結語

采用FPGA技術實現數字基帶傳輸系統,包括編碼器的設計與仿真、譯碼器的設計與仿真以及整個數字基帶傳輸系統的設計與仿真。最后,在Altera公司的ACEX1K-EP1K30TC144-1芯片上加以實現。整個系統具有結構簡單,性能穩定,有效性好,可靠性高等優點。除此之外,其優點還體現在設計者不受芯片結構的影響,避免了重復設計,縮短了開發周期;設計的模塊化,提高了軟硬件的組合度,使設計成果可以重復利用;在選擇實現系統目標器件的類型、規模、硬件結構等方面,具有更大的自由度;總的設計方案和功能結構被確定后,就可以進行多人多任務的并行工作方式,擴大了設計規模,提高了設計效率。

評論