數字基帶傳輸系統的FPGA設計與實現

2 編、譯碼模塊的設計與仿真

編、譯碼模塊的設計是在QuartusⅡ軟件開發平臺上,采用VHDL語言來實現的。

2.1 編碼模塊的設計

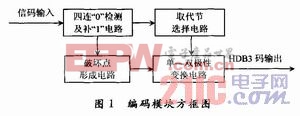

編碼模塊的方框圖如圖1所示。

四連“0”檢測及補“1”電路 根據編碼規則,當輸入的信號遇到四連“0”碼的時候,四連“0”碼將由取代節“B00V”或者“000V”取代。因此,首先要檢測出哪些是四連“0”碼,哪些是非四連“0”碼。在檢測出四連“0”碼后,還要將破壞脈沖V加入在第四個0的位置上。

取代節選擇電路 當需要用取代節代替四連“0”碼時,應判斷采用哪一種取代節,即選擇四連“0”碼中第一個0碼變為B碼,還是變為0碼。如果傳號數為奇數,采用“000V”取代;如果傳號數為偶數,則采用“B00V”取代。

破壞點形成電路 將補放的“1”碼變成破壞點,使后續的V碼與前面相鄰的“1”碼極性相同,破壞了交替反轉的規律,形成了破壞點。

單—雙極性變換電路 HDB3碼極性形成電路有兩個功能:一是正常傳號“B”正負交替極性的形成;二是破壞點“V”脈沖的正負交替極性的形成,并輸出HDB3碼。

2.2 譯碼模塊的設計

譯碼模塊的方框圖如圖2所示。

破壞點檢測電路 即找V碼,在s消息的二進制代碼中,若找出相鄰兩個同極性的碼元,則可以確定后一個碼元必為V碼。

取代節去除電路 在V碼出現時刻將信碼流中的V碼及其前面的第三位碼置為“0”,即去掉取代節。

雙—單極性變換電路 進行全波整流,將“+1”和“-1”還原為1。變換后的碼元即為原信息碼。

2.3 編碼模塊的仿真

根據圖1所示的編碼模塊方框圖在QuartusⅡ平臺上用VHDL語言編程,編譯通過后可進行仿真。

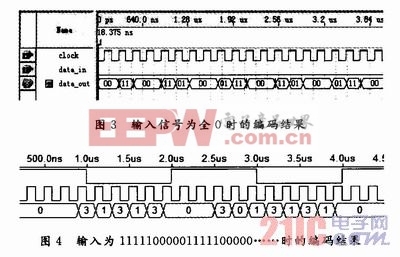

當輸入信碼為全“0”碼時,編碼結果為0-100-1+100+1-100-1+100+1……的序列,如圖3所示。圖中clock為時鐘信號,data_in為輸入信碼,data_out為編碼后的結果。data_out為00,表示“0”電平;data_out為01(十進制數字為1),表示“+1”電平;data_out為11(十進制數字為3),表示“-1”電平。

當輸入信碼為11111000001111100000……時,編碼結果為-1+1-1+1-1000-10+1-1+1-1+1000+1……的序列,如圖4所示。

由圖3,圖4可知,編碼結果完全正確。

評論