基于FPGA的部分響應CPM信號解調器的設計

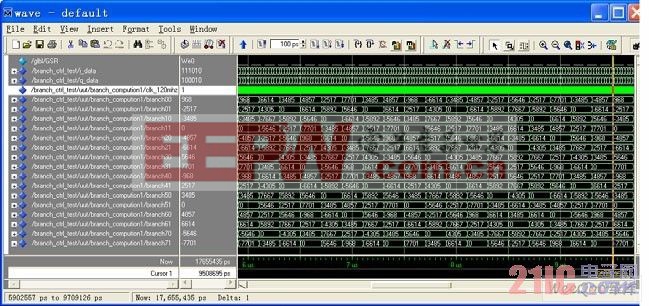

仿真中選擇二進制,關聯長度L 取2,升余弦脈沖的調制方式。仿真中波特率為5 MHz, 采用8 倍采樣,系統時鐘為120 MHz。假設輸入到調制器的雙極性比特流為{ } n b :1,1,1,-1,1,1,-1,-1,1,1,1,-1,1,1,-1,1……分支度量仿真結果如圖3 所示。

圖3 分支度量仿真結果

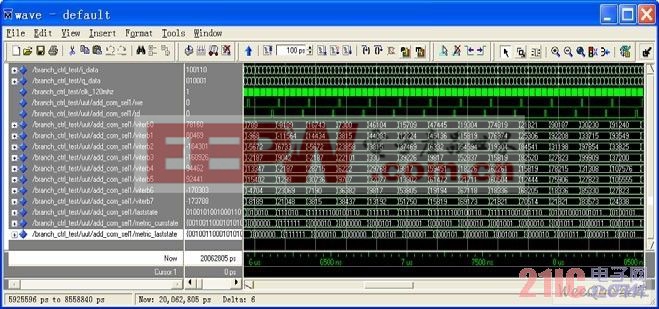

加比選模塊仿真結果如圖4 所示。

圖4 加比選模塊仿真結果

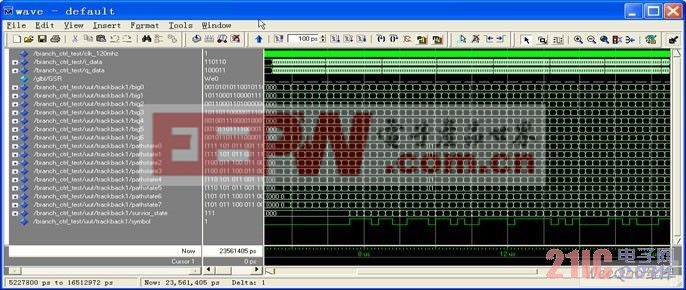

幸存路徑存儲和判決輸出模塊仿真結果如圖5 所示。

圖5 幸存路徑存儲和判決輸出模塊仿真結果

譯碼碼字:1,1,1,-1,1,1,-1,-1,1,1,1,-1,1,1,-1,1……當調制信號不加高斯白噪聲時,實現了誤碼率為0 的解調。仿真結果表明這里所設計的性能達到設計的要求。

4 結語

文中主要設計了該二進制2RC CPM 信號基于FPGA 的解調器。該方法針對Viterb 譯碼方法,提出了一種新的防止路徑度量值溢出方法。該設計的優點是:幸存路徑存儲器中存入的只是路徑信息,不需要存儲路徑度量值,節省了存儲空間;當譯碼輸出時只需要讀出最大路徑度量值的狀態所對應的幸存路徑存儲單元的最低位狀態值,提高了譯碼速度。該方法有效地防止路徑度量值溢出。

評論