基于FPGA的部分響應CPM信號解調器的設計

2 CPM 解調模塊的原理及其實現

2.1 解調器實現原理

對CPM 信號的接收、解調,常采取的步驟為:解調-最大似然序列估計-Viterbi 譯碼-判決。首先將接收到的復包絡信號分為I,Q兩路,下變頻為基帶信號,分別與cos(ψ (t, a))和sin(ψ (t, a))相關后相加,從而得到節點的度量值。對于t時刻每個狀態,可以根據其輸入值的不同,計算來自前一級節點的兩條路徑的路徑度量,并分別加上前一級節點的節點度量,然后從中選擇一個最小的度量值作為節點度量,并存儲前一級節點的信息。

2.2 解調器實現框圖

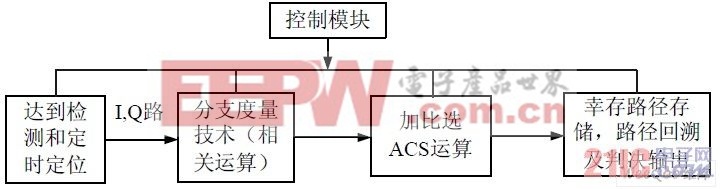

這里仿真采用二進制2RC 的調制方式,根據Viterbi 譯碼方式可知,調制信號共有8 個狀態,將這些狀態分別編碼為000,001,010,011,100,101,110,111。輸入數據與狀態間轉移關系見表1。筆者在設計中將其分為四個模塊:分支度量模塊、加比選模塊、回溯模塊和控制模塊。其結構設計如圖2 所示。

圖2 解調過程

(1)分支度量模塊

此模塊根據輸入數據計算分支度量值。在FPGA設計中,預先將每種基準狀態抽樣時刻的值存入STD 寄存器中,在計算分支度量時通過查表得到基準狀態的值。將輸入I,Q 兩路數據進行串/并轉換,得到一個碼元持續時間內的調制信號后,與每種基準狀態的抽樣值相乘并相加,從而得到I,Q 兩路的路徑度量值。最后將I,Q 兩路度量值相加,便可以得到各狀態的分支度量值。

評論