基于FPGA的高效FIR濾波器設計與實現

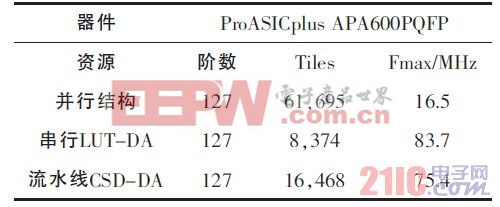

表2所列是不同結構濾波器的綜合結果。其中并行結構是最差的一種結構, 它占用資源多、速度慢; 串行LUT-DA結構, 雖然占用資源少,最大工作頻率高, 但畢竟是串行結構, 不能在一個時鐘節拍完成對一個采樣點的濾波運算; 而流水線CSD-DA結構則無論在速度, 還是面積上,都具有比較明顯的優勢。如果工作時鐘為75MHz, 那么, 一個時鐘節拍便可以完成一次輸出, 處理330個采樣點的單通道信號僅需4.4μs,可以滿足測井實時性要求。

表2 濾波器的綜合結果

4 結果分析

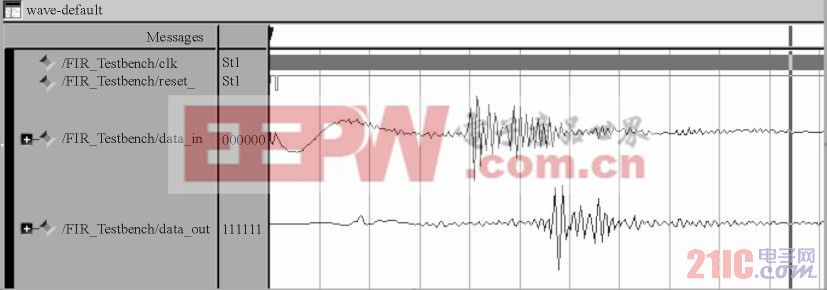

為了驗證濾波器的功能是否正確, 可對本設計在Modelsim中進行仿真。若原始波形為帶噪聲的聲波信號, 那么, 其濾波的結果如圖4所示。

圖4 濾波器在Modelsim中的仿真結果

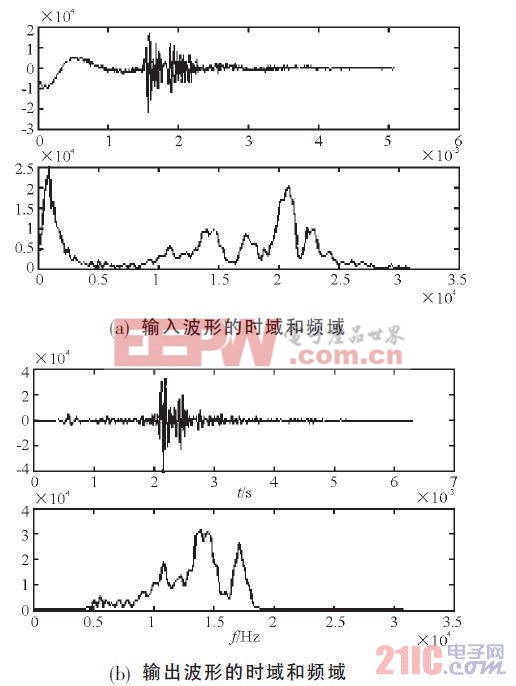

圖5所示是濾波器在Matlab中的仿真結果, 可以看出, Modelsim和Matlab的仿真結果一致。在頻域上, 對比圖5 (a) 和圖5 (b) 可以看到, 其濾波后的波形只保留了5kHz~18kHz的頻譜部分, 這說明流水線CSD-DA結構的數字濾波器設計正確。

圖5 濾波器在Matlab中的仿真結果

5 結束語

本文詳細講述了通過Matlab工具設計FIR線性相位濾波器的方法, 并針對聲波信號設計了優于傳統結構的流水線CSD-DA結構, 該結構具有較明顯的速度和面積優勢。文中也通過仿真實驗證實了設計的合理性和正確性。但值得指出的是, 該結構只適合固定濾波器系數的場合, 而如果要進行修改, 則需要重新對系數進行CSD編碼和流水線分割。

評論