FPGA實現UART和MCU一體化設計

摘要:現代數字電子系統設計正在朝著新的方向發展,即利用FPGA技術進行系境設計。介紹了一種利用FPGA來實現通用串行異步收發器(UA-RT)和控制通信的MCU的數字系統,底層設計模塊采用VHDL硬件描述語言實現,并進行了仿真驗證。該設計方法和理念為以后的計算機系統以及其他的數字電子系統提供了一個新的思路,應用此技術可以使系統設計更加緊湊、可靠。

關鍵詞:計算機系統;FPGA;VHDL;UART;MCU;有限狀態機

計算機技術和微電子技術的發展為現代電子設計提供了新的方法和途徑。傳統的電子設計采用功能獨立的分立元件進行功能組合從而實現特定的功能,計算機設計初期也一直采用這種模式。但是隨著近代電子技術的進步,尤其是FPGA(Field Programmable Gate Array)的出現,使得電子設計和計算機設計都發生了很大的變化,尤其是在數字電子系統的設計領域。利用現場可編程門陣列FPGA可以實現任何數字器件的功能,而且還可以大大縮短設計時間,減少PCB的面積,提高信號的傳輸質量,提高系統的可靠性,增加設計的靈活性和可維護性。本文采用FPGA技術實現一個MCU與串行通信外設進行簡易通信的平臺,一方面了解了計算機的一些控制原理和工作流程;另一方面可以了解利用FPGA進行電子設計的優越性。

1 FPGA與電子設計

用FPGA進行計算機I/O通信設備的開發設計,實現了功能類似Intel 8250及8251,美國半導體公司的16550串行通信接口的功能,同時實現了帶有簡單類忙編指令的微控制單元MCU來控制與外圍I/O設備的通信。整個設計采用VHDL在Altera的QuartusⅡV6.0進行設計實現,并進行仿真驗證。

1.1 FPGA的原理及其開發平臺

通常的FPGA由布線資源分隔的可編程邏輯單元構成陣列,又由司編程I/O單元圍繞陣列構成整個芯片,排成這列的邏輯單元由布線通道中可編程內連線連接來實現一定的邏輯功能,也就是說分段的互連線可以通過可編程開關以任意方式連接起來形成邏輯單元的信號線。一個FPGA主要由邏輯陣列塊(LAB)、I/O塊、RAM塊和可編程的行/列線等組成。

1.2 FPGA的開發軟件及設計流程

FPGA的開發軟件一般由生產FPGA的廠商根據自己的產品特性提供專門的開發工具,目前主要流行的是Xilinx的ISE平臺和Altera的Quar-tus平臺。本文使用的是后者。使用該設計開發軟件能夠完成FPGA系統設計的流程基本包括了設計輸入(原理圖輸入或HDL語言描述輸入)、綜合、布線、下載等工作。本文所設計的電子系統設計輸入采用VHDL語言。

選定了設計平臺后,只要考慮所要設計系統的功能,借助集成開發環境即可完成想要的設計。一般來說,利用FPGA進行電子設計的完整的設計流程分為電路的設計與輸入、功能仿真、綜合、綜合后仿真、實現、布局布線后仿真、配置下載與調試等步驟。由于FPGA的靈活性和設計的可重復性,可以保證在任何仿真或者驗證步驟出現問題時都能根據錯誤定位返回相應的步驟,以進行更改或者重新設計。這是傳統電子設計方法無法比擬的。

2 系統設計與實現

本文所設計的系統實現了一個可簡易匯編指令的微控制器MCU和一個計算機組成中的外圍串行通信I/O設備。通過實現的一部分I/O輸入/輸出指令和條件跳轉指令可實現與外設的通信控制。系統功能模塊劃分如圖1所示。

2.1 串行通信外設的設計與實現

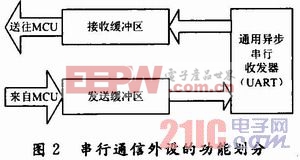

在計算機系統組成中,串行通信占據重要地位,它的使用范圍包括計算機與外部設備之間,計算機與計算機之間、甚至在進行前期CPU設計時都會用到。傳統的設計方法是應用Intel公司的8250/8251或者美國半導體的16550等芯片,但因設計復雜,占用電路體積大,而且出現問題不容易跟蹤定位,所以本文采用FPGA實現。將串行通信的關鍵器件UART集成到FPGA內部,增加系統的可靠性,縮小PCB板體積,使得系統更加緊致,且能根據需要進行適當的設計、擴充和裁剪。實現的該I/O設備功能劃分如圖2所示。

評論