高階FIR濾波器的計算機設計與FPGA實現

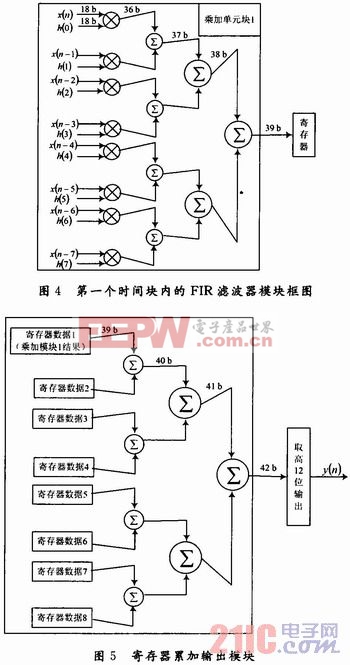

以本文設計的FIR濾波器為例(后面詳述),輸入信號的速率為2 MHz(周期為500 ns),濾波器的階數為64階,由此構造了8個乘法器(最多可以構造25個),分8次完成所有的乘法。相對分布式算法的流水速度而言,構造的乘法器完成一次乘法需要20 ns,相對耗時長一點,但是完成8次乘法也只需8×20=160 ns,小于輸入信號一個周期的時間,因此滿足設計需求。將輸入數據的一個周期平均分為8個時間塊,每個時間內的FIR濾波設計模塊的框圖如圖4所示。本文引用地址:http://www.104case.com/article/191265.htm

其他7個時間塊內的FIR濾波器模塊同圖4,所不同的是參與乘法運算的信號輸入數據和濾波器抽頭系數不同,分別從x(n-8)到x(n-63)和h(8)到h(63)。待8個乘加模塊的結果均送入寄存器后,再在最后一個時間塊內完成累加得到最終的輸出(相對乘法運算而言,完成累加的時間可以忽略),其實現框圖如圖5。

結合圖4和圖5,可全部完成基于LPM參數化宏功能模塊的FIR濾波器設計。由兩圖可以發現,有多個全加器,且輸入數據的位數(bit數)不同,只要調節LPM宏功能模塊的參數即可方便地完成設計,輸出數據y(n)的位數則根據工程需要取最終累加結果的高12位。取高12位帶來的誤差為![]() (最高位為符號位,不予數值考慮),這是可以接受的誤差。

(最高位為符號位,不予數值考慮),這是可以接受的誤差。

2 基于Matlab和QuartusⅡ的FIR濾波器設計

2.1 利用Matlab進行濾波器系數設計

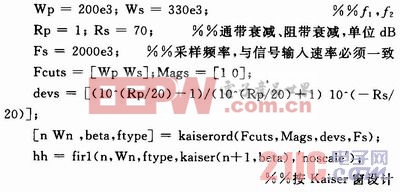

設計指標:采樣頻率為2 MHz,f1=200 kHz,f2=330 kHz,通帶衰減1 dB,阻帶衰減70 dB。通過參數指標確定所需的階數和參數值,部分程序如下:

評論