基于FPGA和LabView的遙測信號模擬源設計

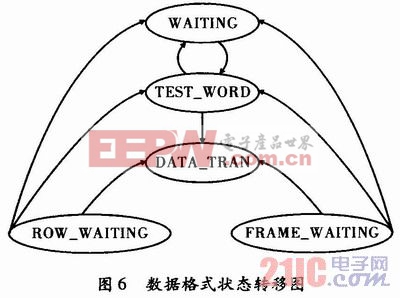

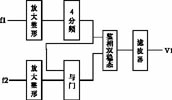

發送數據時控制單元將從單口RAM中讀取的待發送數據存放在FPGA中的乒乓RAM中,并串轉換后發送數據。FPGA讀取外部RAM數據存入乒乓RAM的時間必須小于并串轉換后發送8位數據的時間,否則會造成數據丟失。發送的數據格式通過有限狀態機控制,狀態轉移圖,如圖6所示。本文引用地址:http://www.104case.com/article/191246.htm

3 結果測試

本設計FPGA芯片采用Altera公司的EP2C8Q208C8,使用QuatusⅡ8.1開發系統實現編程和仿真,完成對電路設計的功能和時序分析。

在QuatusⅡ中編譯工程后,建立SignalTapⅡ文件并加入工程、配置STP文件、編譯并將STP文件同原有的設計下載到FPGA中。人機交互界面設置發送頻率為5 MHz,圖像數據為循環發送0~127,數字量信息字為0~253,點擊LVDS開始按鈕。通過SignalTapⅡ窗口下查看邏輯分析儀實時捕獲的數據,格式與要求完全一致,發送數據正確。實時捕獲數據,如圖7所示。另外,SignalTapⅡ中設置的采樣時鐘頻率要大于被測信號最高頻率的2倍,否則無法正確反映被測信號波形的變化,測試完畢后要將該邏輯分析儀從項目中刪除。

4 結束語

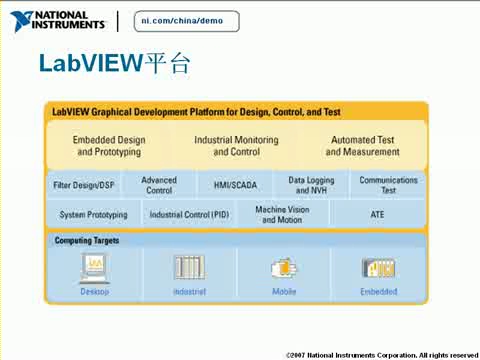

文中探討了基于FPGA和LabView的遙測信號模擬源的設計,采用了“FPGA+接口+PC”的設計方案,實現了由PC程控、傳輸速率4~8MHz、固定幀格式的LVDS信號。通過此方法可以在短時間內構建一個通用靈活的虛擬儀器平臺,接口可以根據實際條件采用USB、串口、紅外等多種方式。

評論